R01UH0823EJ0100 Rev.1.00

Page 1011 of 1823

Jul 31, 2019

RX23W Group

33. Serial Communications Interface (SCIg, SCIh)

33.2.26

Interrupt Control Register (ICR)

Address(es): SCI12.ICR 0008 B326h

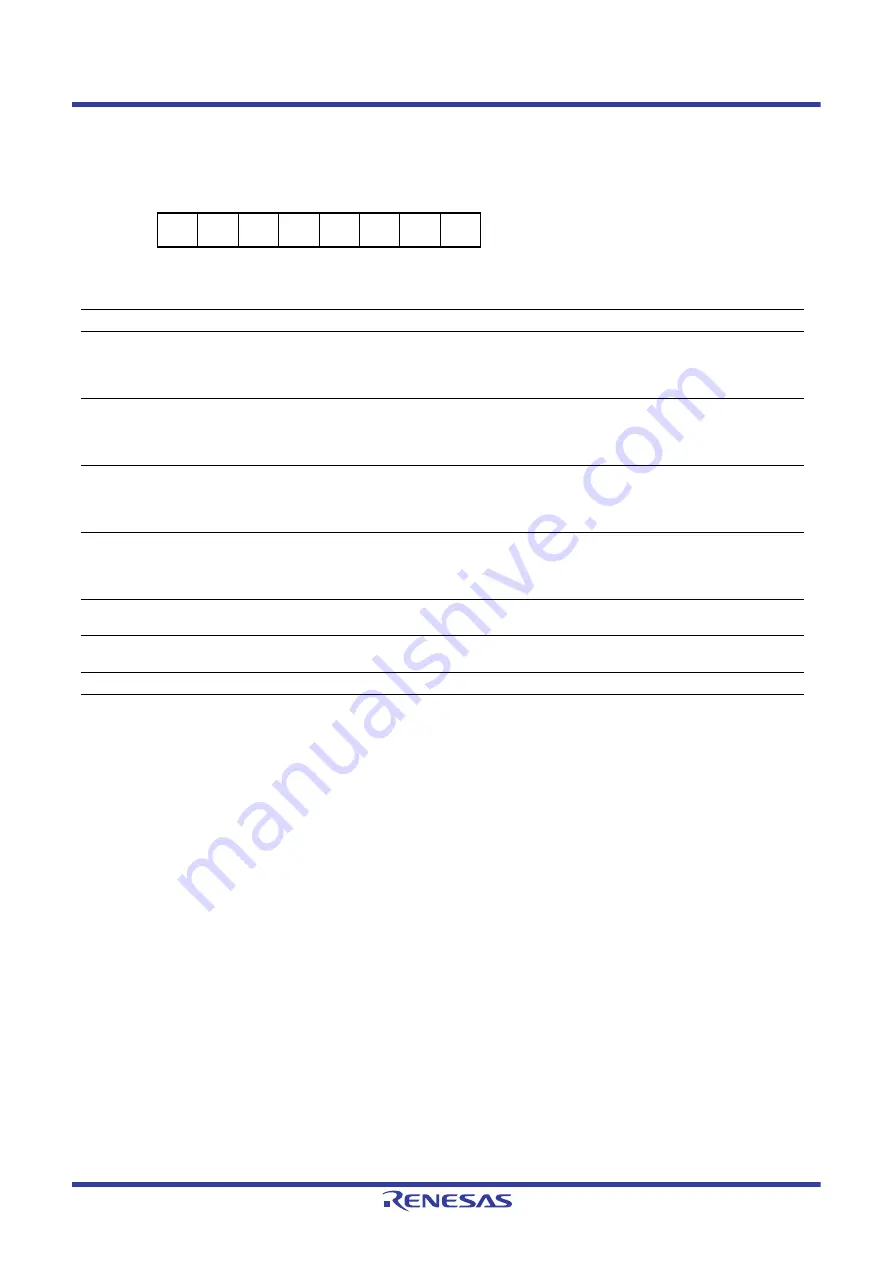

b7

b6

b5

b4

b3

b2

b1

b0

—

—

AEDIE BCDIE PIBDIE CF1MI

E

CF0MI

E

BFDIE

Value after reset:

0

0

0

0

0

0

0

0

Bit

Symbol

Bit Name

Description

R/W

b0

Break Field Low Width Detected

Interrupt Enable

0: Interrupts on detection of the low width for a Break Field

are disabled.

1: Interrupts on detection of the low width for a Break Field

are enabled.

R/W

b1

Control Field 0 Match Detected

Interrupt Enable

0: Interrupts on detection of a match with Control Field 0 are

disabled.

1: Interrupts on detection of a match with Control Field 0 are

enabled.

R/W

b2

Control Field 1 Match Detected

Interrupt Enable

0: Interrupts on detection of a match with Control Field 1 are

disabled.

1: Interrupts on detection of a match with Control Field 1 are

enabled.

R/W

b3

Priority Interrupt Bit Detected Interrupt

Enable

0: Interrupts on detection of the priority interrupt bit are

disabled.

1: Interrupts on detection of the priority interrupt bit are

enabled.

R/W

b4

Bus Collision Detected Interrupt Enable 0: Interrupts on detection of a bus collision are disabled.

1: Interrupts on detection of a bus collision are enabled.

R/W

b5

Valid Edge Detected Interrupt Enable

0: Interrupts on detection of a valid edge are disabled.

1: Interrupts on detection of a valid edge are enabled.

R/W

b7, b6

—

Reserved

These bits are read as 0. The write value should be 0.

R/W