R01UH0823EJ0100 Rev.1.00

Page 742 of 1823

Jul 31, 2019

RX23W Group

26. 8-Bit Timer (TMR)

26.4.2

Timing of Interrupt Signal Output on a Compare Match

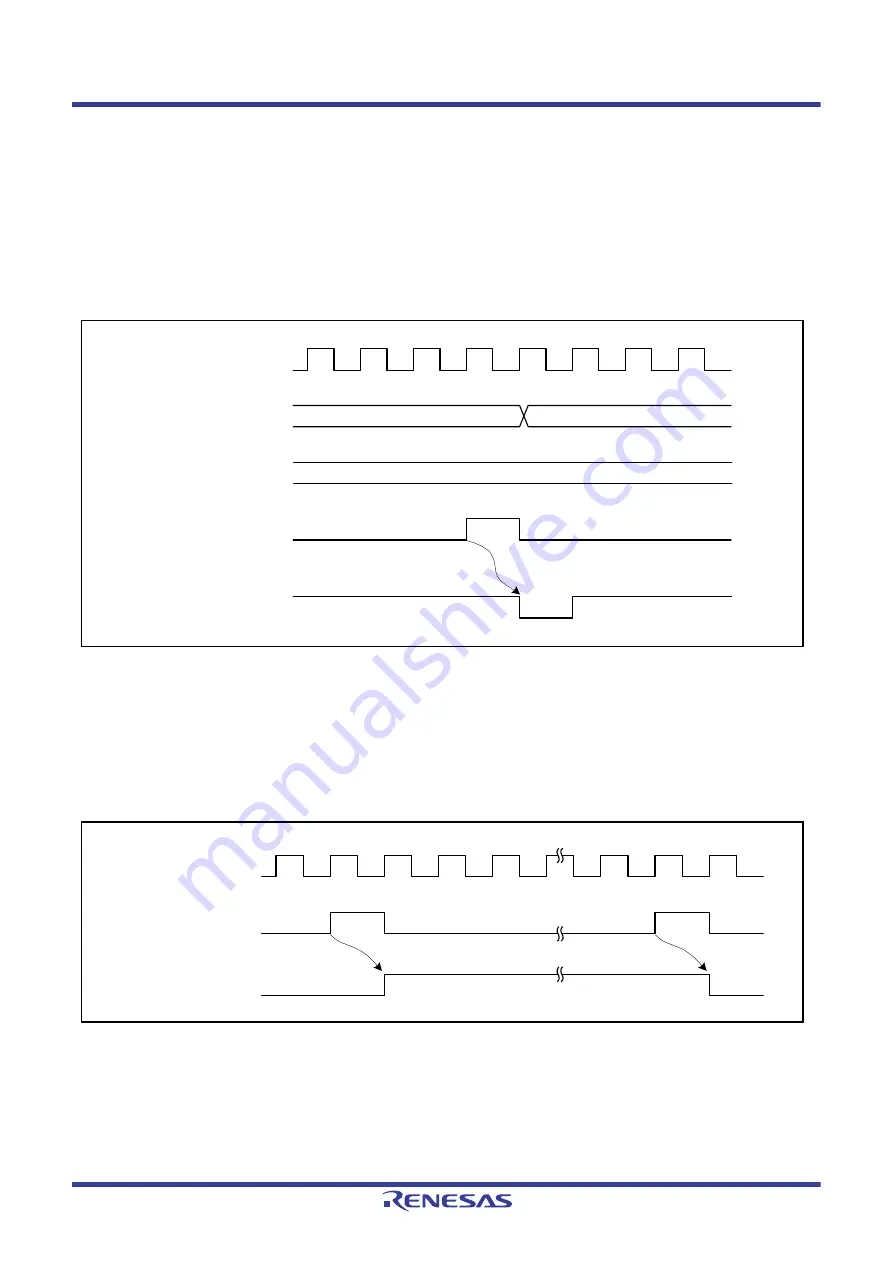

A compare match refers to a match between the value of the TCORA or TCORB register and the TCNT, and a compare

match interrupt signal is output at this time if the interrupt request is enabled. The compare match is generated in the last

cycle in which the values match (at the time at which the value counted by TCNT to produce the match is updated).

Accordingly, after a match between TCNT and the TCORA or TCORB register is detected, the compare match is not

actually generated until the next cycle of the TCNT count clock.

shows the timing of output of the interrupt

signal.

For the corresponding interrupt vector number, refer to

section 15, Interrupt Controller (ICUb)

and

Figure 26.7

Timing of Interrupt Flag Setting to 1 at Compare Match (n = 0 to 3)

26.4.3

Timing of Timer Output Signal at Compare Match

When a compare match signal is generated, the output value specified by the TCSR.OSA[1:0] and OSB[1:0] bits is

output on the timer output pin (TMOn).

shows the timing when the timer output is toggled by the compare match A signal.

Figure 26.8

Timing of Timer Output Signal at Compare Match A Signal (n = 0 to 2)

Internal compare match

signal

TCORA or TCORB

PCLK

TCNT

CMIAn or CMIBn

N + 1

N

N

Compare match A signal

TMOn

PCLK