R01UH0823EJ0100 Rev.1.00

Page 267 of 1823

Jul 31, 2019

RX23W Group

14. Exception Handling

14.6

Return from Exception Handling Routine

Executing the instruction listed in

at the end of the corresponding exception handling routine restores the

values of the program counter (PC) and processor status word (PSW) that were saved on the stack or in the control

registers (BPC and BPSW) immediately before the exception handling sequence.

14.7

Priority of Exception Events

The priority of exception events is listed in

. When multiple exceptions are generated at the same time, the

exception with the highest priority is accepted first.

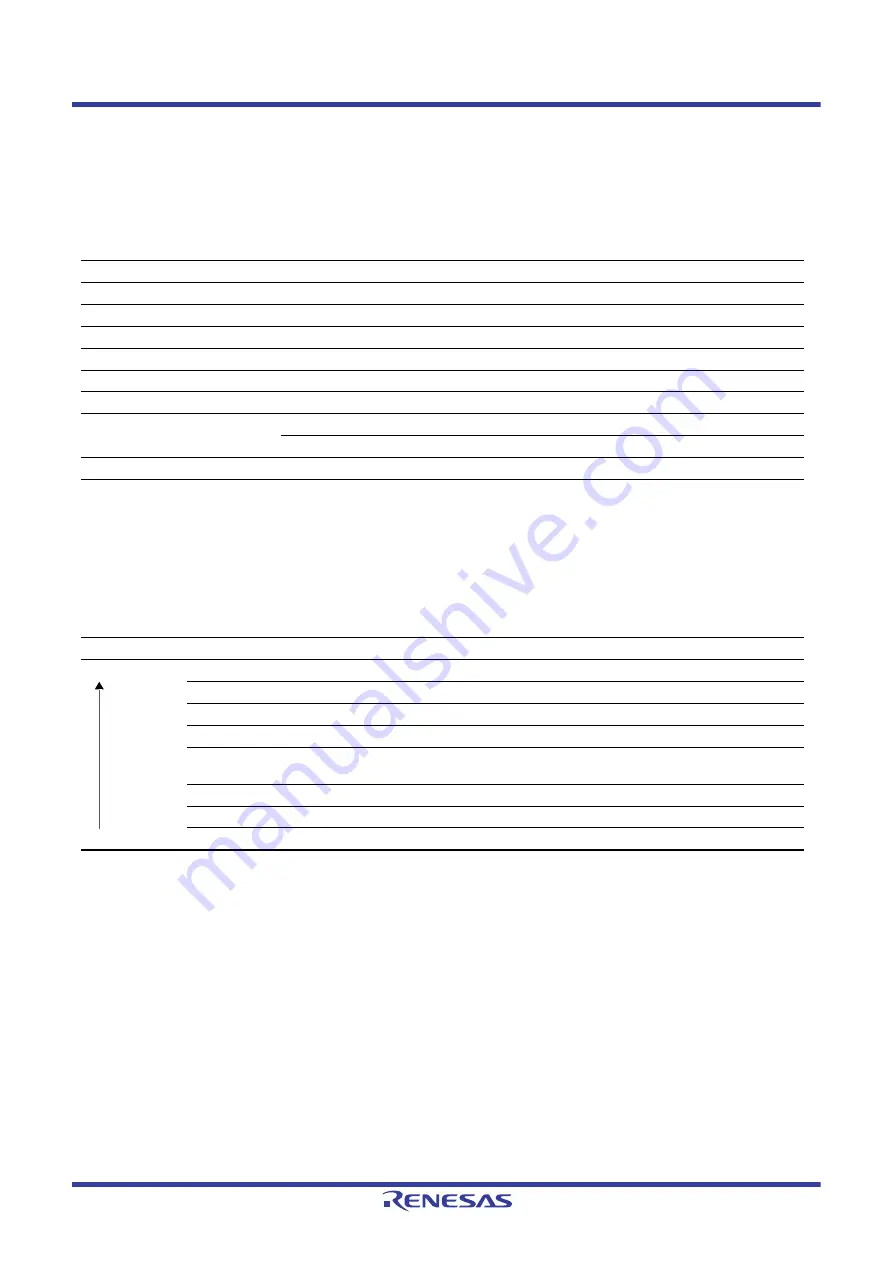

Table 14.3

Return from Exception Handling Routine

Exception

Instruction for Return

Undefined instruction exception

RTE

Privileged instruction exception

RTE

Access exception

RTE

Floating-point exception

RTE

Reset

Return is impossible

Non-maskable interrupt

Prohibited

Interrupt

Fast interrupt

RTFI

Other than above

RTE

Unconditional trap

RTE

Table 14.4

Priority of Exception Events

Priority

Exception Event

High

Low

1

Reset

2

Non-maskable interrupt

3

Interrupt

4

Instruction access exception

5

Undefined instruction exception

Privileged instruction exception

6

Unconditional trap

7

Operand access exception

8

Floating-point exception