R01UH0823EJ0100 Rev.1.00

Page 1207 of 1823

Jul 31, 2019

RX23W Group

36. CAN Module (RSCAN)

36.2.12

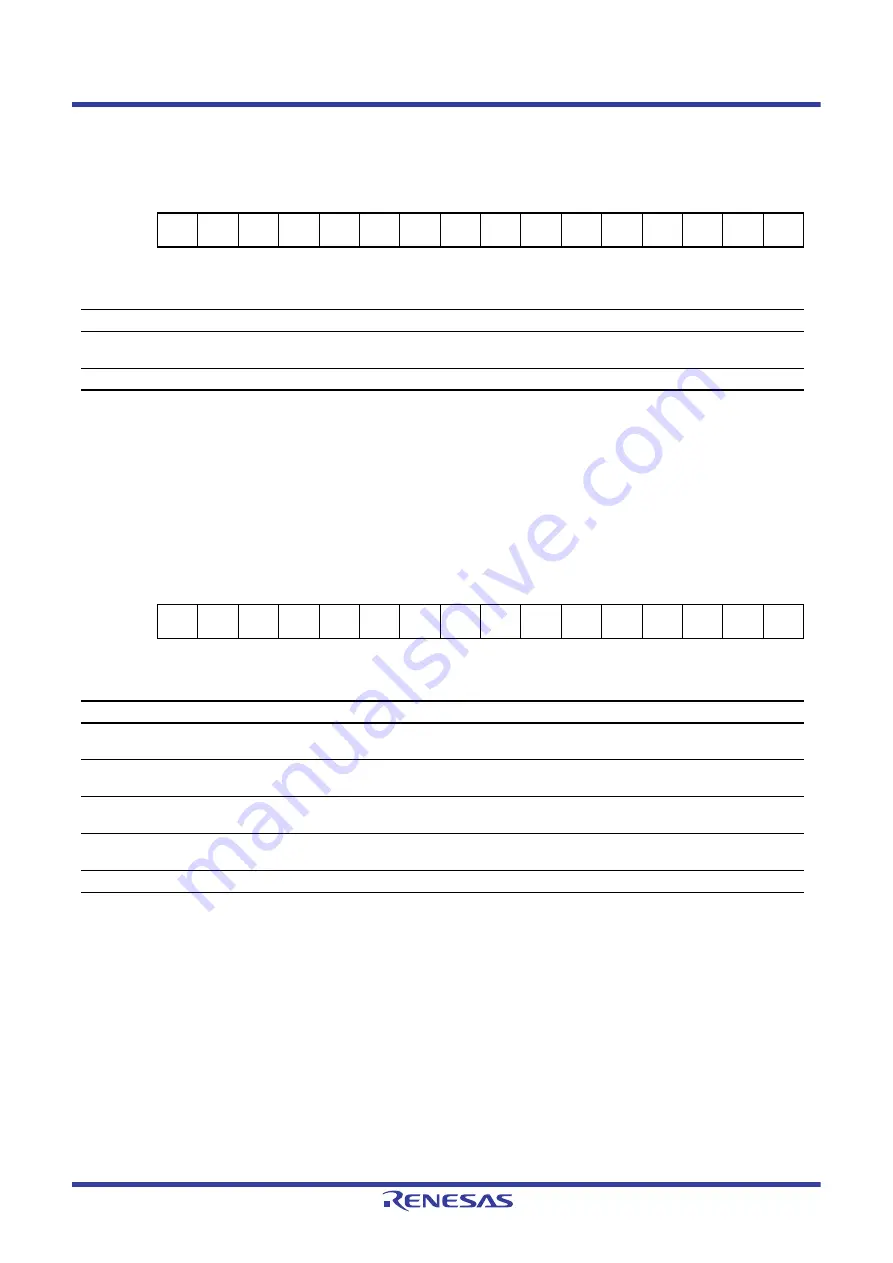

Global Control Register H (GCTRH)

TSRST Bit (Timestamp Counter Reset)

This bit is used to reset the timestamp counter. When this bit is set to 1, the GTSC register is set to 0000h.

36.2.13

Global Status Register (GSTS)

GRSTSTS Flag (Global Reset Status Flag)

This flag becomes 1 when the CAN module has transitioned to global reset mode, and becomes 0 when the CAN module

has exited global reset mode. This flag remains 1 even when the CAN module has transitioned from global reset mode to

global stop mode.

GHLTSTS Flag (Global Test Status Flag)

This flag becomes 1 when the CAN module has transitioned to global test mode, and becomes 0 when the CAN module

has exited global test mode.

GSLPSTS Flag (Global Stop Status Flag)

This flag becomes 1 when the CAN module has transitioned to global stop mode, and becomes 0 when the CAN module

Address(es): RSCAN.GCTRH 000A 8328h

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

TSRST

Value after reset:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Symbol

Bit Name

Description

R/W

b0

Timestamp Counter Reset

Setting the TSRST bit to 1 resets the timestamp counter.

This bit is read as 0.

R/W

b15 to b1

—

Reserved

These bits are read as 0. The write value should be 0.

R/W

Address(es): RSCAN.GSTS 000A 832Ah

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

—

—

—

—

—

—

—

—

—

—

—

—

GRAMI

NIT

GSLPS

TS

GHLTS

TS

GRSTS

TS

Value after reset:

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

1

Bit

Symbol

Bit Name

Description

R/W

b0

Global Reset Status Flag

0: Not in global reset mode

1: In global reset mode

R

b1

Global Test Status Flag

0: Not in global test mode

1: In global test mode

R

b2

Global Stop Status Flag

0: Not in global stop mode

1: In global stop mode

R

b3

CAN RAM Initialization Status

Flag

0: CAN RAM initialization is completed.

1: CAN RAM initialization is ongoing.

R

b15 to b4

—

Reserved

These bits are read as 0.

R