R01UH0823EJ0100 Rev.1.00

Page 1460 of 1823

Jul 31, 2019

RX23W Group

40. SD Host Interface (SDHIa)

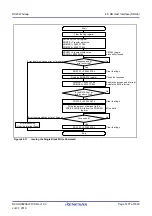

40.3.6.6 Multi-Block Write Command (CMD25)

shows an example of issuing the multi-block write command (CMD25).

1. Set the flags in registers SDSTS1 and SDSTS2 to 0.

2. Set the SDHI clock in the SDCLKCR register, and set the interrupt requests to be masked in registers SDIMSK1

for details on setting the SDCLKCR register. Set the

SDSTOP.SDBLKCNTEN bit to 1, and set the number of transfer blocks in the SDBLKCNT register.

3. After setting the argument field value for CMD25 to the SDARG register, write 0000 0019h to the SDCMD

register. The SDHI issues CMD25 when a value is written to the SDCMD register.

4. When the response is received, the SDSTS1.RSPEND flag becomes 1, and the response end interrupt request is

generated.

5. Set the SDSTS1.RSPEND flag to 0 and read the response stored in the SDRSP54 register. If the read response is in

error, set the SDSTOP.STP bit to 1, and the command sequence can be stopped. When the SDSTOP.STP bit is set to

1, the SDHI automatically issues CMD12, and the response is received. At this point, the SDSTS1.ACEND flag

becomes 1, and if the access end interrupt request is enabled, the access end interrupt request is generated. Next, set

the SDSTS1.ACEND flag to 0 and read the response.

6. After the response is received, configure the SDIMSK1 register to enable the access end interrupt request, and

configure the SDIMSK2 register to enable the BWE interrupt request.

7. When the SDBUFR register becomes write accessible, the SDSTS2.BWE flag becomes 1, and the BWE interrupt

request is generated.

8. Set the SDSTS2.BWE flag to 0, and write the amount of data set in the SDSIZE.LEN[9:0] bits to the SDBUFR

register. After writing to the SDBUFR register, and after the SDHI transmits write data to the SD card, the CRC

status token is received, and the SDHI_D0 pin line becomes busy (low). The write access to the SDBUFR register

and CRC status token reception repeat for the amount of transfer blocks set in the SDBLKCNT register. Also, after

writing to the SDBUFR register, data transmission may cause a communication error or timeout to occur. After the

amount of transfer blocks set in the SDBLKCNT register have been written, the SDHI automatically issues

CMD12, and the response is received. At that time, the SDHI automatically writes 0000 0000h to the SDARG

register.

9. When all blocks have been transmitted and the CRC status token is received, the SDHI exits the busy state, the

SDSTS1.ACEND flag becomes 1, and the access end interrupt request is generated.

10. Set the SDSTS1.ACEND flag to 0 and read the response.

Perform error processing (clear the interrupt flag) if a communication error or timeout occurs.