R01UH0823EJ0100 Rev.1.00

Page 343 of 1823

Jul 31, 2019

RX23W Group

18. DMA Controller (DMACA)

18.2.4

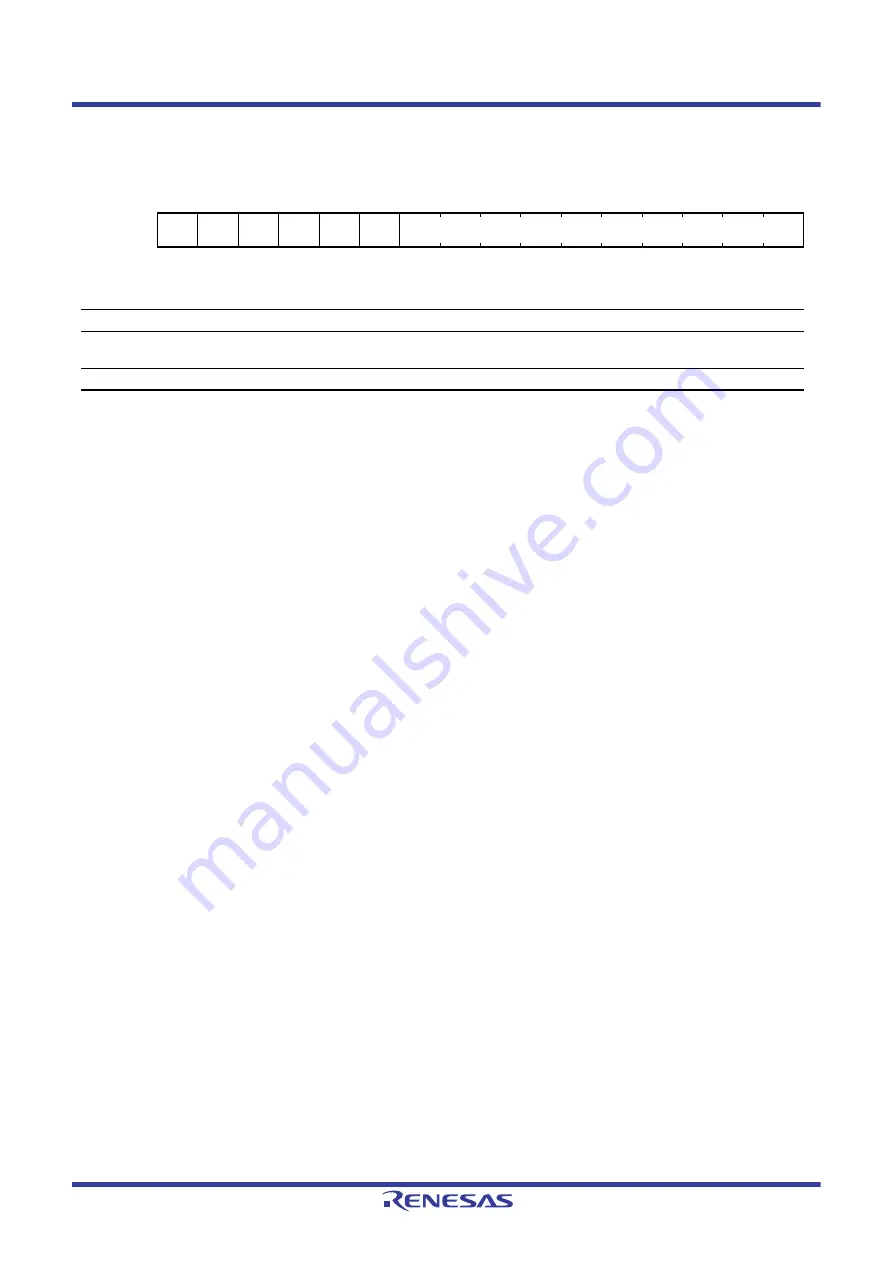

DMA Block Transfer Count Register (DMCRB)

DMCRB specifies the number of block transfer operations and repeat transfer operations in block and repeat transfer

mode, respectively.

The number of transfer operations is one when the setting is 001h, 1023 when it is 3FFh, and 1024 when it is 000h.

In repeat transfer mode, the value is decremented by one when the final data of one repeat size is transferred.

In block transfer mode, the value is decremented by one when the final data of one block size is transferred.

In normal transfer mode, DMCRB is not used. The setting is invalid.

Address(es): DMAC0.DMCRB 0008 200Ch, DMAC1.DMCRB 0008 204Ch, DMAC2.DMCRB 0008 208Ch, DMAC3.DMCRB 0008 20CCh

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

—

—

—

—

—

—

Value after reset:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit

Description

Setting Range

R/W

b9 to b0

Specifies the number of block transfer operations

or repeat transfer operations.

001h to 3FFh (1 to 1023)

000h (1024)

R/W

b15 to b10

Reserved

These bits are read as 0. The write value should be 0.

R/W