R01UH0823EJ0100 Rev.1.00

Page 751 of 1823

Jul 31, 2019

RX23W Group

26. 8-Bit Timer (TMR)

26.8.6

Conflict between Compare Matches A and B

If compare match events A and B occur at the same time, the 8-bit timer operates in accordance with the priorities for the

output methods high for compare match A and compare match B, as listed in

26.8.7

Switching of Internal Clocks and TCNT Operation

TCNT may be incremented erroneously depending on when the internal clock is switched.

lists the

relationship between the timing at which the internal clock is switched (by writing to the TCCR.CKS[2:0] bits) and the

operation of TCNT.

When TCNT count clock is generated from an internal clock, the rising edge of the internal clock pulse are always

monitored. If the signal levels of the clocks before and after switching change from low to high as shown in No. 2 in

, the change is considered as an edge. Therefore, a TCNT count clock is generated and TCNT is incremented.

The erroneous increment of TCNT can also happen when switching between internal and internal clocks.

Table 26.7

Timer Output Priorities

Output Setting

Priority

Toggle output

High

Low

High output

Low output

No change

Table 26.8

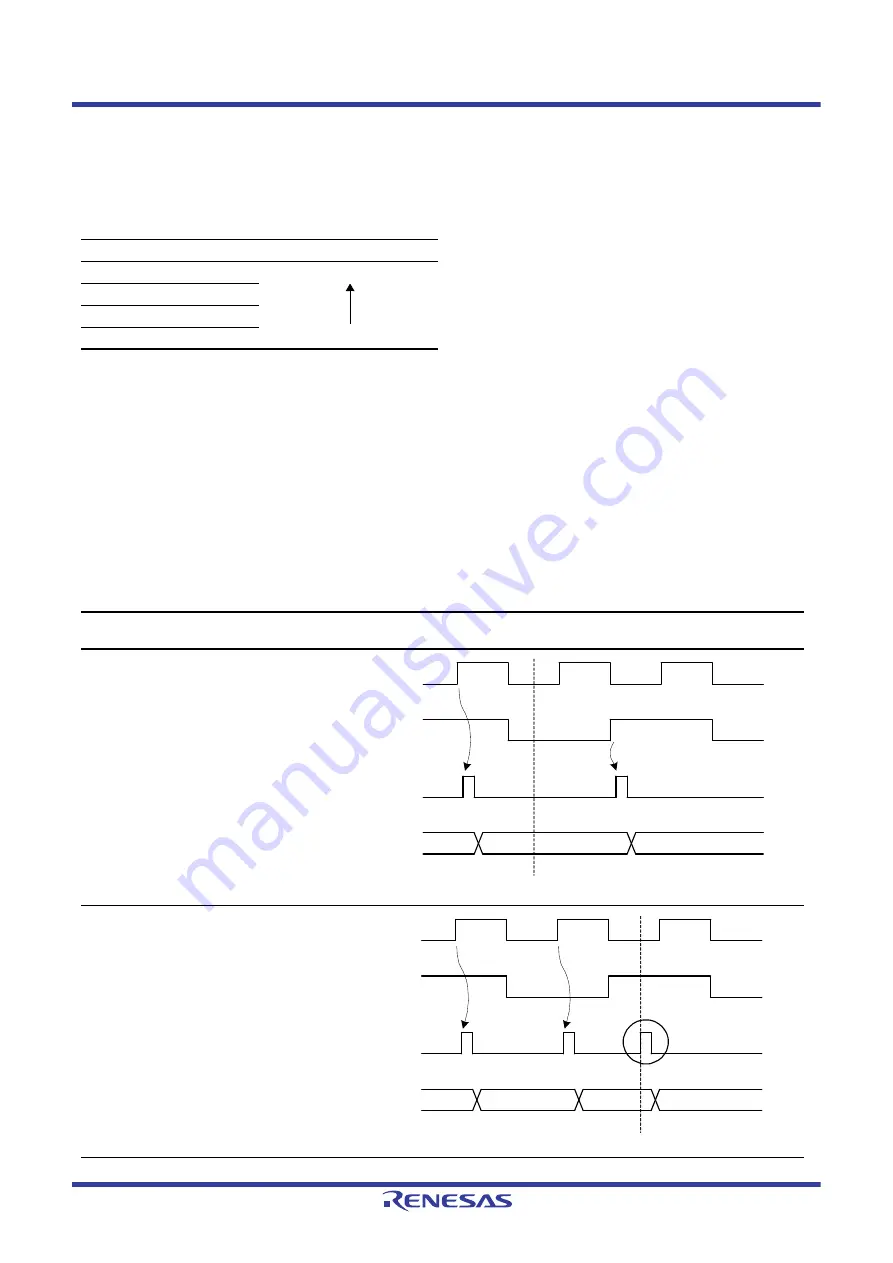

Switching of Internal Clocks and TCNT Operation (1/2)

No.

Timing to Change the

TCCR.CKS[2:0] Bits

TCNT Counter Operation

1

Switching from low to low*

2

Switching from low to high*

Clock before

switching

Clock after

switching

TCNT count

clock

TCNT

TCCR.CKS[2:0] bits changed

N + 1

N

N + 2

Clock before

switching

Clock after

switching

TCNT count

clock

TCNT

TCCR.CKS[2:0] bits changed

*3

N + 1

N

N + 2

N + 3