R01UH0823EJ0100 Rev.1.00

Page 361 of 1823

Jul 31, 2019

RX23W Group

18. DMA Controller (DMACA)

18.3.2

Extended Repeat Area Function

The DMAC supports a function to specify the extended repeat areas on the transfer source and destination addresses.

With the extended repeat areas set, the address registers repeatedly indicate the addresses of the specified extended repeat

areas.

The extended repeat areas can be specified separately to the transfer source address register (DMSAR) and transfer

destination address register (DMDAR) of DMACm.

The extended repeat area on the source address is specified by the SARA[4:0] bits in DMAMD of DMACm. The

extended repeat area on the destination address is specified by the DARA[4:0] bits in DMAMD of DMACm. The size

can be specified separately for the source and destination sides.

However, the area (of transfer source or transfer destination) which is specified as the repeat area or block area should

not be specified as the extended repeat area.

When the address register value reaches the end address of the extended repeat area and the extended repeat area

overflows, DMA transfer is stopped and an interrupt by an extended repeat area overflow can be requested. When an

overflow occurs in the extended repeat area on the transfer source while the SARIE bit in DMINT of DMACm is set to 1,

the ESIF flag in DMSTS of DMACm is set to 1 and the DTE bit in DMCNT of DMACm is cleared to 0 to stop DMA

transfer. At this time, if the ESIE bit in DMINT of DMACm is set to 1, an interrupt by an extended repeat area overflow

is requested. When the DARIE bit in DMINT of DMACm is set to 1, the destination address register becomes a target to

apply the function. DMA transfer can be resumed by writing 1 to the DTE bit in DMCNT of DMACm in the interrupt

handling.

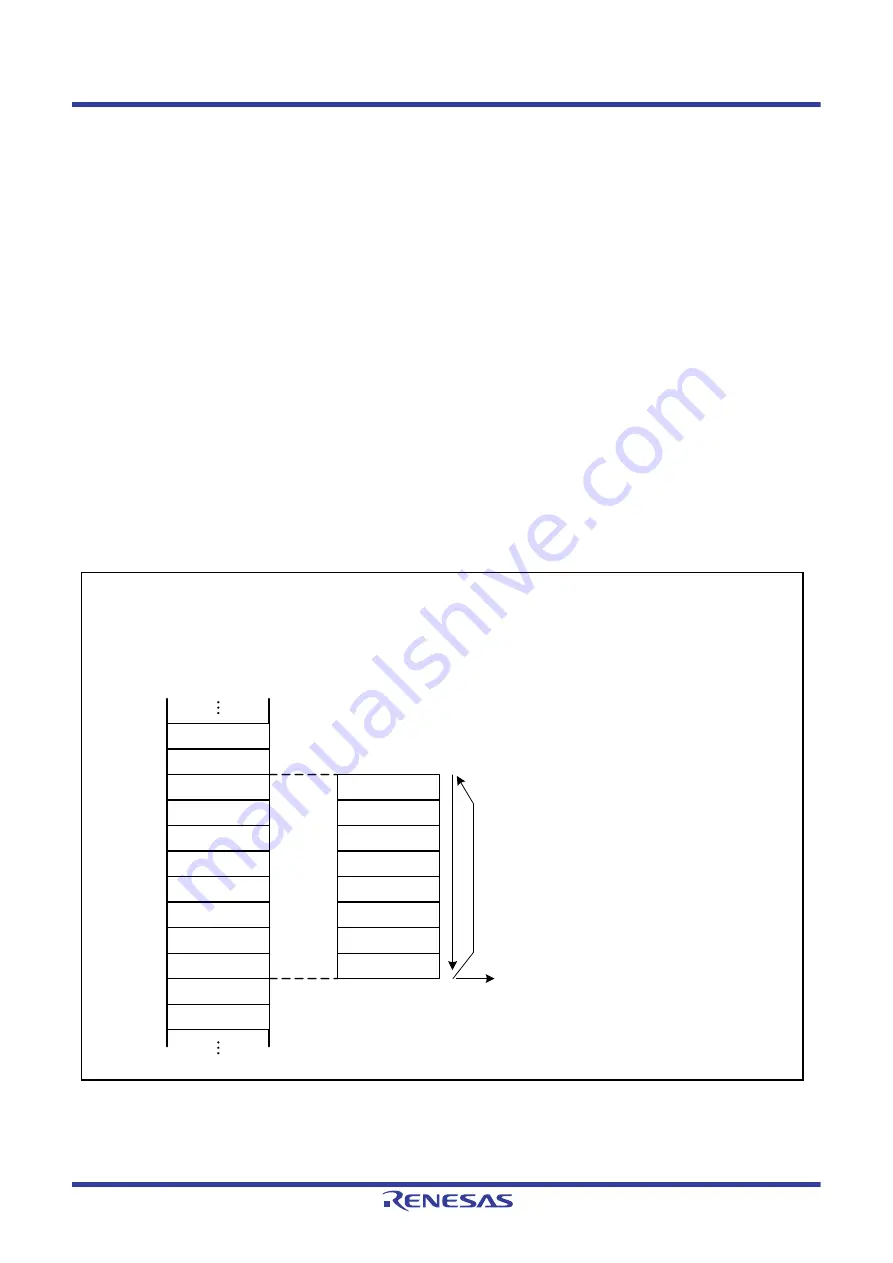

shows an example of the extended repeat area operation.

Figure 18.5

Example of Extended Repeat Area Operation

Example:

Eight bytes are specified as an extended repeat area by the lower three bits of DMACm.DMSAR (SARA[4:0]

bits in DMACm.DMAMD = 00011b).

The data size is eight bits (SZ[1:0] bits in DMACm.DMTMD = 00b).

Memory area

Repeat

00013FFEh

00013FFFh

00014000h

00014001h

00014002h

00014003h

00014004h

00014005h

00014006h

00014007h

00014008h

00014009h

00014000h

00014001h

00014002h

00014003h

00014004h

00014005h

00014006h

00014007h

An extended repeat area overflow interrupt

request can be generated.

DMSAR value

range