R01UH0823EJ0100 Rev.1.00

Page 674 of 1823

Jul 31, 2019

RX23W Group

25. 16-Bit Timer Pulse Unit (TPUa)

25.2.4

Timer Interrupt Enable Register (TIER)

Note 1. These bits are reserved in TPU1, TPU2, TPU4, and TPU5. These bits are read as 0. The write value should be 0.

Note 2. This bit is reserved in TPU0 and TPU3. This bit is read as 0. The write value should be 0.

Note 3. This bit is reserved in TPU5. This bit is read as 0. The write value should be 0.

TTGE Bit (A/D Conversion Start Request Enable)

Enables/disables generation of A/D conversion start requests by TPUm.TGRA (m = 0 to 4) input capture/compare

match.

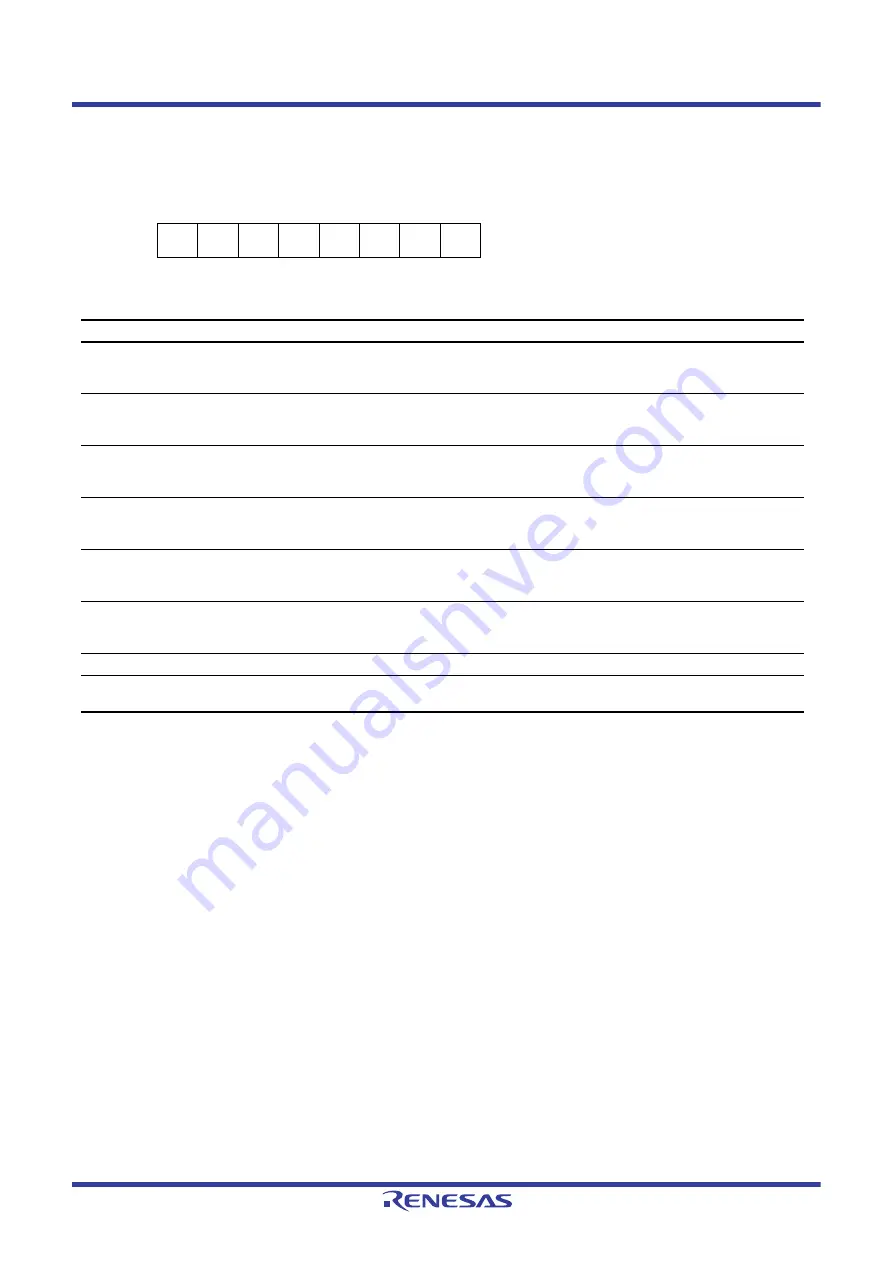

Address(es): TPU0.TIER 0008 8114h, TPU1.TIER 0008 8124h, TPU2.TIER 0008 8134h,

TPU3.TIER 0008 8144h, TPU4.TIER 0008 8154h, TPU5.TIER 0008 8164h

b7

b6

b5

b4

b3

b2

b1

b0

TTGE

—

TCIEU TCIEV TGIED TGIEC TGIEB TGIEA

Value after reset:

0

1

0

0

0

0

0

0

Bit

Symbol

Bit Name

Description

R/W

b0

TGRA Interrupt Enable

0: Interrupt requests (TGImA) disabled

1: Interrupt requests (TGImA) enabled

(m = 0 to 5)

R/W

b1

TGRB Interrupt Enable

0: Interrupt requests (TGImB) disabled

1: Interrupt requests (TGImB) enabled

(m = 0 to 5)

R/W

b2

TGRC Interrupt Enable*

0: Interrupt requests (TGImC) disabled

1: Interrupt requests (TGImC) enabled

(m = 0, 3)

R/W

b3

TGRD Interrupt Enable*

0: Interrupt requests (TGImD) disabled

1: Interrupt requests (TGImD) enabled

(m = 0, 3)

R/W

b4

Overflow Interrupt Enable

0: Interrupt requests (TCImV) disabled

1: Interrupt requests (TCImV) enabled

(m = 0 to 5)

R/W

b5

Underflow Interrupt Enable*

0: Interrupt requests (TCImU) disabled

1: Interrupt requests (TCImU) enabled

(m = 1, 2, 4, 5)

R/W

b6

—

Reserved

This bit is read as 1. The write value should be 1.

R/W

b7

A/D Conversion Start Request Enable*

0: A/D conversion start request generation disabled

1: A/D conversion start request generation enabled

R/W