R01UH0823EJ0100 Rev.1.00

Page 180 of 1823

Jul 31, 2019

RX23W Group

9. Clock Generation Circuit

9.2.8

Sub-Clock Oscillator Control Register (SOSCCR)

Note:

Set the PRCR.PRC0 bit to 1 (write enabled) before rewriting this register.

SOSTP Bit (Sub-Clock Oscillator Stop)

This bit runs or stops the sub-clock oscillator.

The SOSTP bit and the sub-clock oscillator control bit in RTC control register 3 (RCR3.RTCEN) controls whether to

operate or stop the sub-clock oscillator. If one of these bits is set so as to enable the operation, the sub-clock oscillator

runs.

When changing the value of the SOSTP bit or RCR3.RTCEN bit, execute subsequent instructions after reading the bit

and checking that its value has actually been updated (refer to (2), Notes on writing to I/O registers, in

).

After the setting of the SOSTP bit or the RCR3.RTCEN bit has been changed so that the sub-clock oscillator operates,

only start using the sub-clock after the sub-clock oscillation stabilization time (t

SUBOSC

) has elapsed.

That is, a fixed time for stabilization is required after the setting for sub-clock oscillator operation. A fixed time is also

required for oscillation to stop after the setting to stop the oscillator. Accordingly, take note of the following limitations

when starting and stopping the oscillator.

When restarting the sub-clock oscillator after it has been stopped, allow at least five cycles of the sub-clock as an

interval over which it is still stopped.

Ensure that oscillation by the sub-clock oscillator is stable when making the setting to stop the sub-clock oscillator.

Regardless of whether or not it is selected as the system clock, ensure that oscillation by the sub-clock oscillator is

stable before executing a WAIT instruction to place the chip on software standby.

When a transition to software standby mode is to follow the setting to stop the sub-clock oscillator, wait for at least

two cycles of the sub-clock oscillator after the setting to stop the sub-clock oscillator and before executing the

WAIT instruction.

While the sub-clock oscillator is selected by the SCKCR3.CKSEL[2:0] bits, do not set the SOSTP bit to 1 (sub-clock

oscillator is stopped).

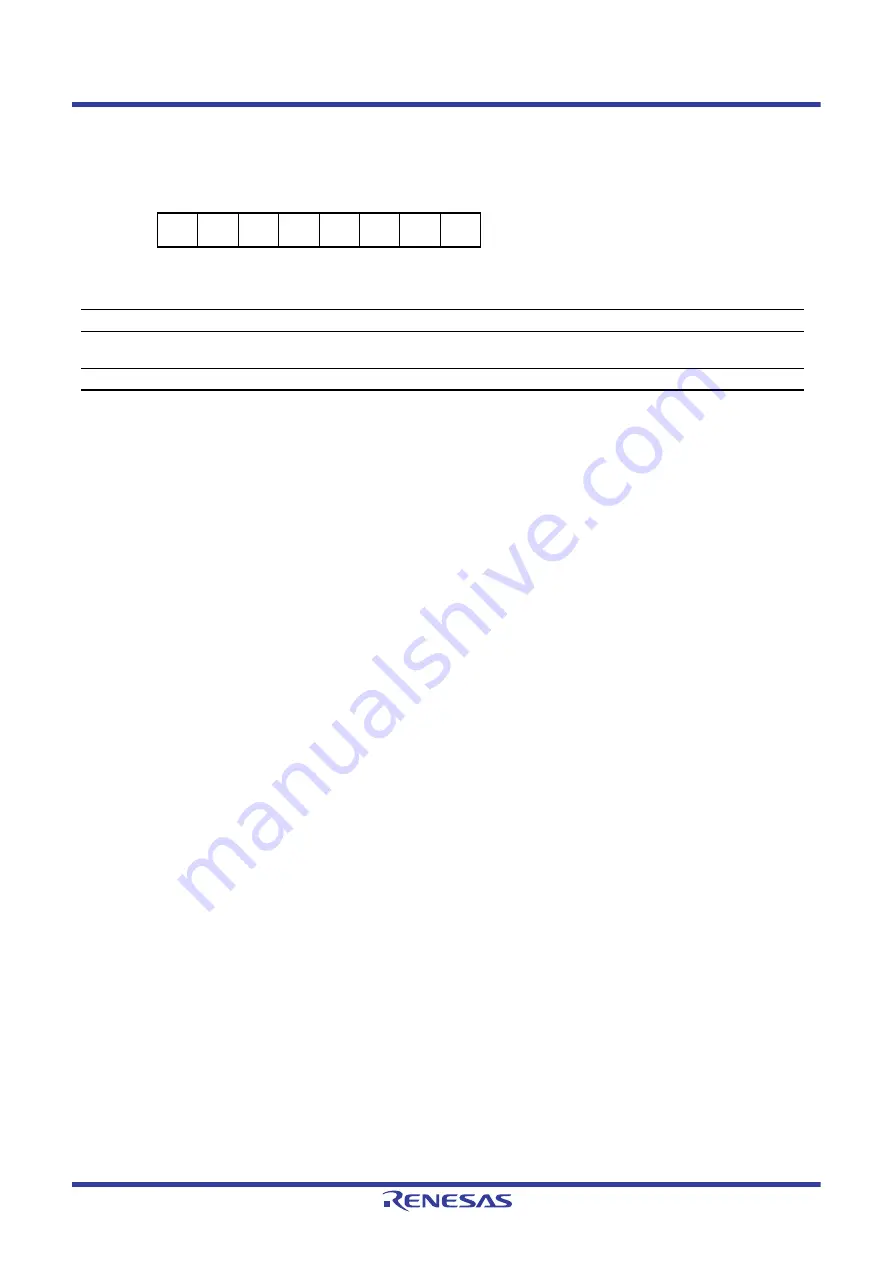

Address(es): 0008 0033h

b7

b6

b5

b4

b3

b2

b1

b0

—

—

—

—

—

—

—

SOSTP

Value after reset:

0

0

0

0

0

0

0

0

Bit

Symbol

Bit Name

Description

R/W

b0

Sub-Clock Oscillator Stop

0: Sub-clock oscillator is operating.

1: Sub-clock oscillator is stopped.

R/W

b7 to b1

—

Reserved

These bits are read as 0. The write value should be 0.

R/W