R01UH0823EJ0100 Rev.1.00

Page 838 of 1823

Jul 31, 2019

RX23W Group

31. Independent Watchdog Timer (IWDTa)

TOPS[1:0] Bits (Timeout Period Select)

These bits select the timeout period (period until the counter underflows) from among 128, 512, 1024, or 2048 cycles,

taking the divided clock specified by the CKS[3:0] bits as one cycle.

After the counter is refreshed, the combination of the CKS[3:0] and TOPS[1:0] bits determines the time (number of

IWDTCLK cycles) until the counter underflows.

Relations between the CKS[3:0] and TOPS[1:0] bit setting, the timeout period, and the number of IWDTCLK cycles are

listed in

CKS[3:0] Bits (Clock Divide Ratio Select)

These bits select the IWDTCLK clock divide ratio from among divide-by 1, 16, 32, 64, 128, and 256. Combination with

the TOPS[1:0] bit setting, a count period between 128 and 524288 cycles of the IWDTCLK clock can be selected for the

IWDT.

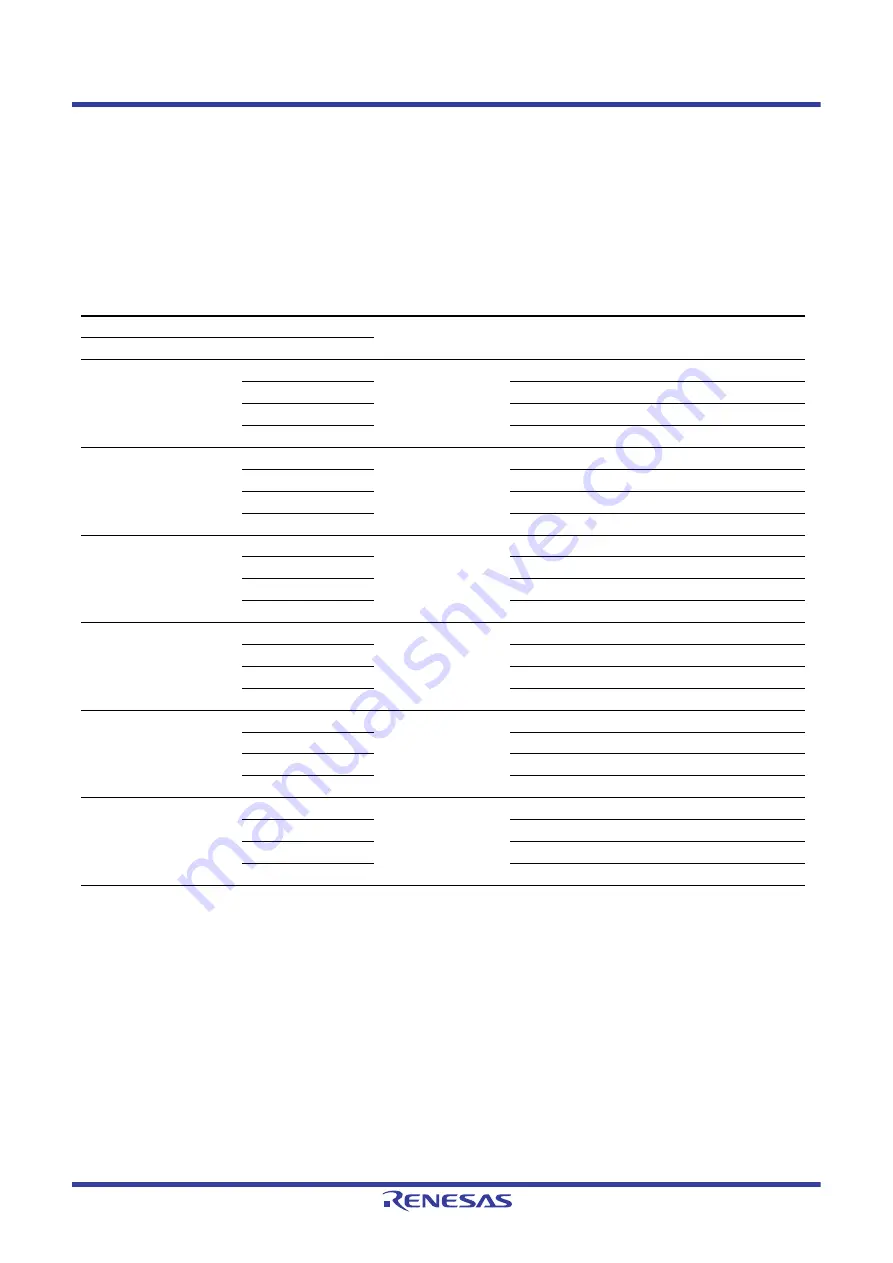

Table 31.2

Settings and Timeout Periods

CKS[3:0] Bits

TOPS[1:0] Bits

Clock Divide Ratio

Timeout Period

(Number of Cycles)

Cycles of IWDTCLK

b7

b6

b5

b4

b1

b0

0

0

0

0

0

0

No division

128

128

0

1

512

512

1

0

1024

1024

1

1

2048

2048

0

0

1

0

0

0

Divide-by-16

128

2048

0

1

512

8192

1

0

1024

16384

1

1

2048

32768

0

0

1

1

0

0

Divide-by-32

128

4096

0

1

512

16384

1

0

1024

32768

1

1

2048

65536

0

1

0

0

0

0

Divide-by-64

128

8192

0

1

512

32768

1

0

1024

65536

1

1

2048

131072

1

1

1

1

0

0

Divide-by-128

128

16384

0

1

512

65536

1

0

1024

131072

1

1

2048

262144

0

1

0

1

0

0

Divide-by-256

128

32768

0

1

512

131072

1

0

1024

262144

1

1

2048

524288