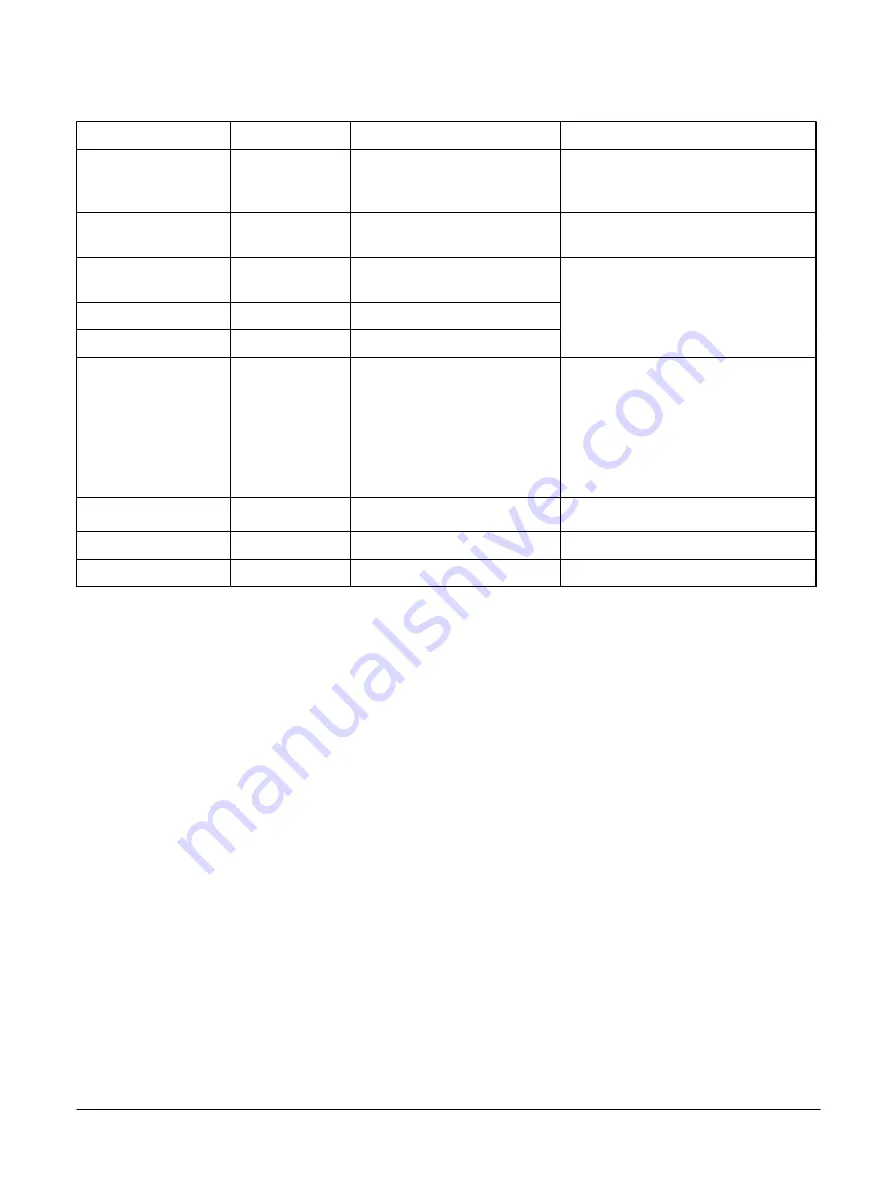

Table A8-1 Cache protection behavior (continued)

RAM

Protection type

Protection granule

Correction behavior

L1 data cache data

SECDED

32 bits of data +1 poison bit + 7 bits

for ECC attached to the word.

The cache line that contains the error gets

evicted, corrected in line, and refilled to the

core.

L1 Prefetch History Table

(PHT)

None

-

-

MMU translation cache

2 interleaved parity

bits

67 bits

Entry invalidated, new pagewalk started to

refetch it.

MMU replacement policy None

-

MMU biased replacement None

-

L2 cache tag

SECDED

128KB L2 - 7 ECC bits for 38 tag

bits

256KB L2 - 7 ECC bits for 37 tag

bits

512KB L2 - 7 ECC bits for 36 tag

bits

Tag is corrected inline.

L2 cache data

SECDED

8 ECC bits for 64 data bits

Data is corrected inline.

L2 victim

None

-

-

L2 TQ data

SECDED

8 ECC bits for 64 data bits

Data is corrected inline.

To ensure that progress is guaranteed even in case of hard error, the core returns corrected data to the

core, and no cache access is required after data correction.

A8 Reliability, Availability, and Serviceability (RAS)

A8.2 Cache protection behavior

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

A8-104

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......