D9.2

TRCACATRn, Address Comparator Access Type Registers 0-7

The TRCACATRn control the access for the corresponding address comparators.

Bit field descriptions

The TRCACATRn is a 64-bit register.

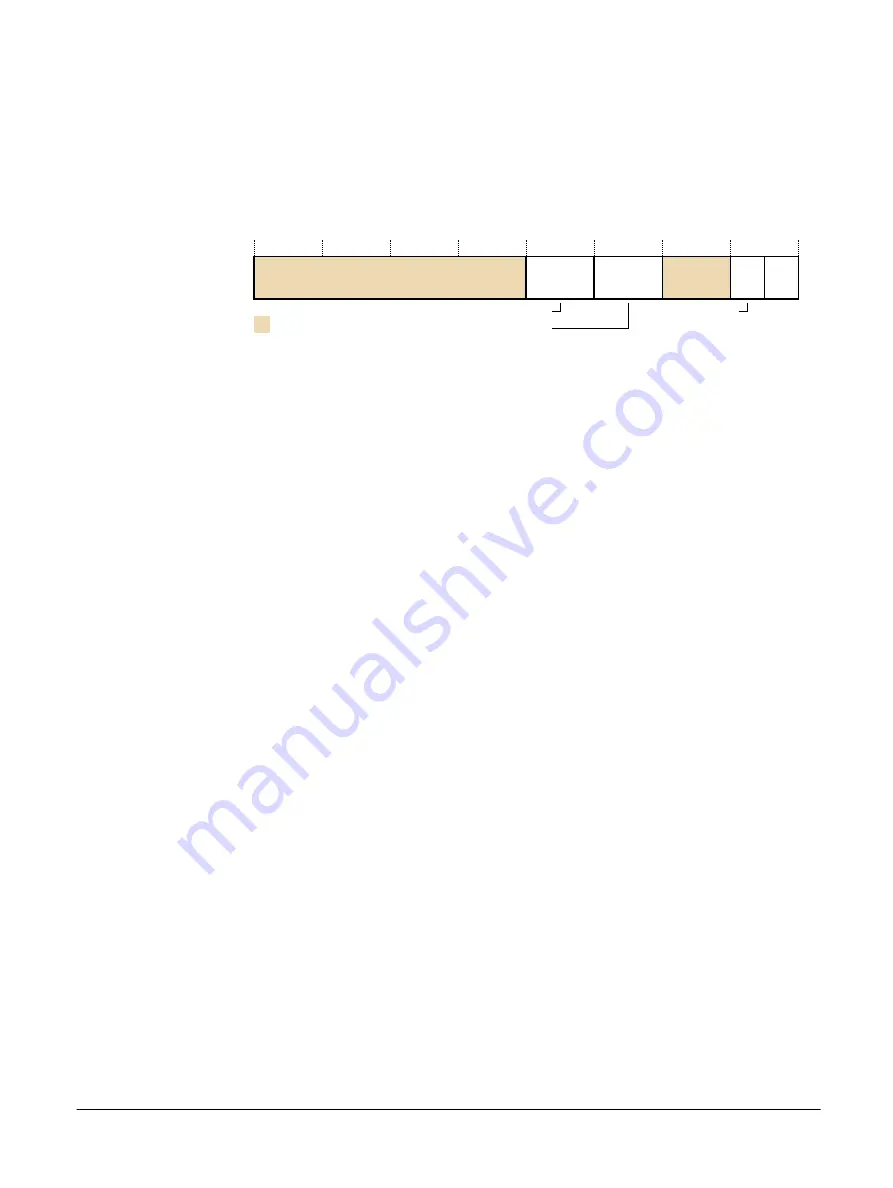

63

16 15

12 11

8 7

3 2 1 0

TYPE

EXLEVEL_S

CONTEXTTYPE

EXLEVEL_NS

RES

0

Figure D9-1 TRCACATRn bit assignments

RES0, [63:16]

RES0

Reserved.

EXLEVEL_NS, [15:12]

Each bit controls whether a comparison can occur in Non-secure state for the corresponding

exception level. The possible values are:

0

The trace unit can perform a comparison, in Non-secure state, for exception level

n

.

1

The trace unit does not perform a comparison, in Non-secure state, for exception level

n

.

The Exception levels are:

Bit[12]

Exception level 0.

Bit[13]

Exception level 1.

Bit[14]

Exception level 2.

Bit[15]

Always

RES0

.

EXLEVEL_S, [11:8]

Each bit controls whether a comparison can occur in Secure state for the corresponding

exception level. The possible values are:

0

The trace unit can perform a comparison, in Secure state, for exception level

n

.

1

The trace unit does not perform a comparison, in Secure state, for exception level

n

.

The Exception levels are:

Bit[8]

Exception level 0.

Bit[9]

Exception level 1.

Bit[10]

Always

RES0

.

Bit[11]

Exception level 3.

RES0, [7:4]

RES0

Reserved.

CONTEXT TYPE, [3:2]

Controls whether the trace unit performs a Context ID comparison, a VMID comparison, or both

comparisons:

D9 ETM registers

D9.2 TRCACATRn, Address Comparator Access Type Registers 0-7

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D9-499

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......