D2.1

AArch64 debug register summary

These registers, listed in the following table, are accessed by the

MRS

and

MSR

instructions in the order of

Op0, CRn, Op1, CRm, Op2.

D3.1 Memory-mapped debug register summary

for a complete list of registers

accessible from the external debug interface. The 64-bit registers cover two addresses on the external

memory interface. For those registers not described in this chapter, see the

Arm

®

Architecture Reference

Manual Armv8, for Armv8-A architecture profile

.

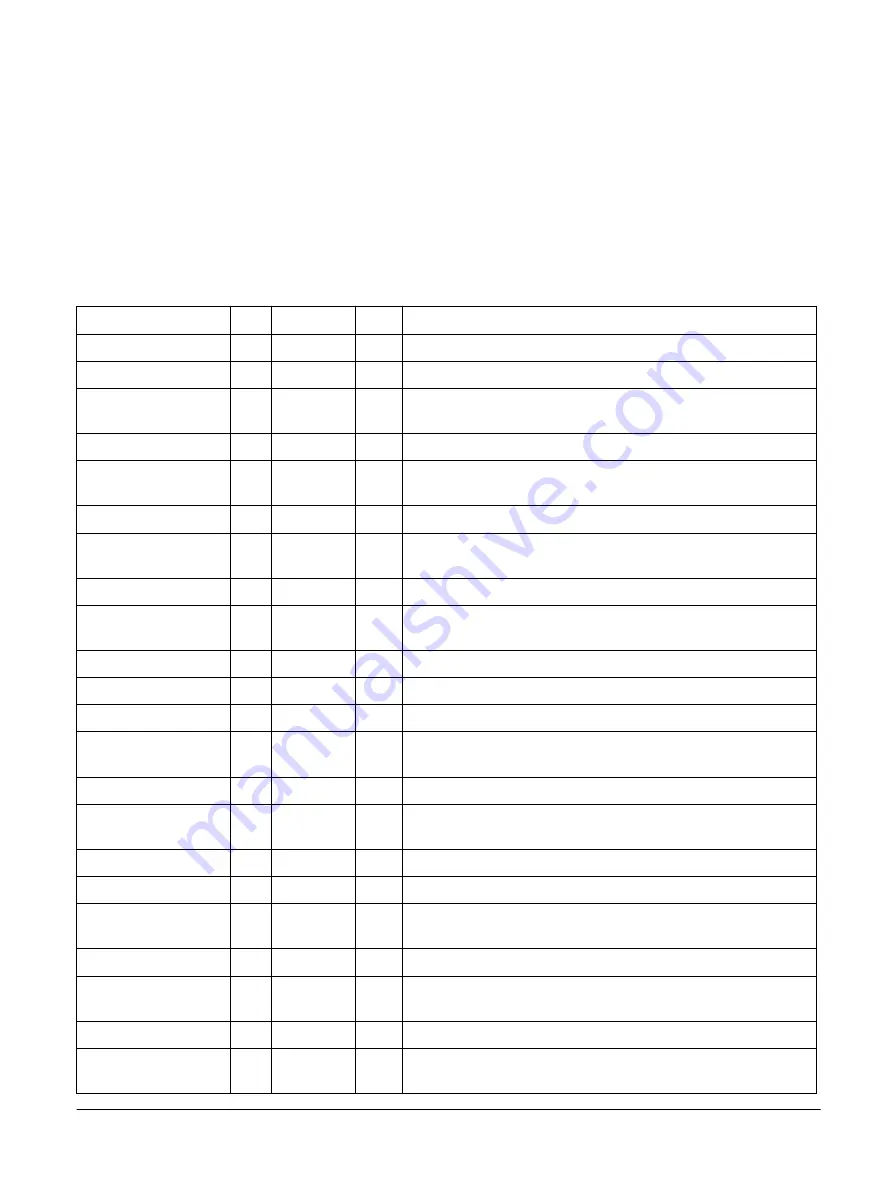

Table D2-1 AArch64 debug register summary

Name

Type Reset

Width Description

OSDTRRX_EL1

RW

0x00000000

32

Debug Data Transfer Register, Receive, External View

DBGBVR0_EL1

RW

-

64

Debug Breakpoint Value Register 0

DBGBCR0_EL1

RW

UNK

32

D2.2 DBGBCRn_EL1, Debug Breakpoint Control Registers, EL1

DBGWVR0_EL1

RW

-

64

Debug Watchpoint Value Register 0

DBGWCR0_EL1

RW

UNK

32

D2.4 DBGWCRn_EL1, Debug Watchpoint Control Registers, EL1

DBGBVR1_EL1

RW

-

64

Debug Breakpoint Value Register 1

DBGBCR1_EL1

RW

UNK

32

D2.2 DBGBCRn_EL1, Debug Breakpoint Control Registers, EL1

DBGWVR1_EL1

RW

-

64

Debug Watchpoint Value Register 1

DBGWCR1_EL1

RW

UNK

32

D2.4 DBGWCRn_EL1, Debug Watchpoint Control Registers, EL1

MDCCINT_EL1

RW

0x00000000

32

Monitor Debug Comms Channel Interrupt Enable Register

MDSCR_EL1

RW

-

32

DBGBVR2_EL1

RW

-

64

Debug Breakpoint Value Register 2

DBGBCR2_EL1

RW

UNK

32

D2.2 DBGBCRn_EL1, Debug Breakpoint Control Registers, EL1

DBGWVR2_EL1

RW

-

64

Debug Watchpoint Value Register 2

DBGWCR2_EL1

RW

UNK

32

D2.4 DBGWCRn_EL1, Debug Watchpoint Control Registers, EL1

OSDTRTX_EL1

RW

-

32

Debug Data Transfer Register, Transmit, External View

DBGBVR3_EL1

RW

-

64

Debug Breakpoint Value Register 3

DBGBCR3_EL1

RW

UNK

32

D2.2 DBGBCRn_EL1, Debug Breakpoint Control Registers, EL1

DBGWVR3_EL1

RW

-

64

Debug Watchpoint Value Register 3

DBGWCR3_EL1

RW

UNK

32

D2.4 DBGWCRn_EL1, Debug Watchpoint Control Registers, EL1

DBGBVR4_EL1

RW

-

64

Debug Breakpoint Value Register 4

DBGBCR4_EL1

RW

UNK

32

D2.2 DBGBCRn_EL1, Debug Breakpoint Control Registers, EL1

D2 AArch64 debug registers

D2.1 AArch64 debug register summary

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D2-406

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......