B3.3

ERR0CTLR, Error Record Control Register

The ERR0CTLR contains enable bits for the node that writes to this record:

• Enabling error detection and correction.

• Enabling an error recovery interrupt.

• Enabling a fault handling interrupt.

• Enabling error recovery reporting as a read or write error response.

Bit field descriptions

ERR0CTLR is a 64-bit register and is part of the

Reliability, Availability, Serviceability

(RAS) registers

functional group.

ERR0CTLR resets to CFI [8], FI [3], and UI [2] are

UNKNOWN

. The rest of the register is

RES0

.

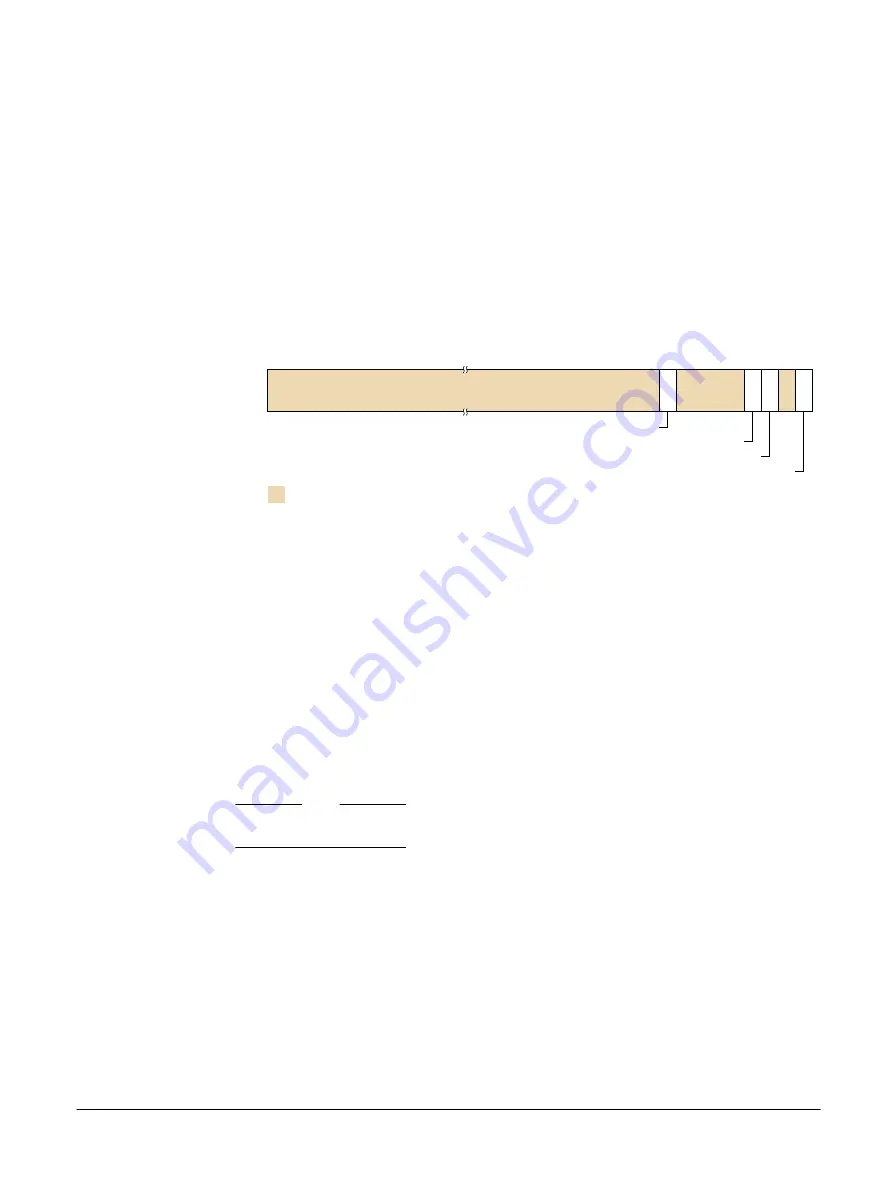

63

9 8 7

4 3 2 1 0

CFI

FI

UI

ED

RES

0

Figure B3-2 ERR0CTLR bit assignments

RES0, [63:9]

RES0

Reserved.

CFI, [8]

Fault handling interrupt for corrected errors enable.

The fault handling interrupt is generated when one of the standard CE counters on ERR0MISC0

overflows and the overflow bit is set. The possible values are:

0

Fault handling interrupt not generated for corrected errors.

1

Fault handling interrupt generated for corrected errors.

The interrupt is generated even if the error status is overwritten because the error record already

records a higher priority error.

Note

This applies to both reads and writes.

RES0, [7:4]

RES0

Reserved.

FI, [3]

Fault handling interrupt enable.

The fault handling interrupt is generated for all detected Deferred errors and Uncorrected errors.

The possible values are:

0

Fault handling interrupt disabled.

1

Fault handling interrupt enabled.

UI, [2]

B3 Error system registers

B3.3 ERR0CTLR, Error Record Control Register

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B3-294

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......