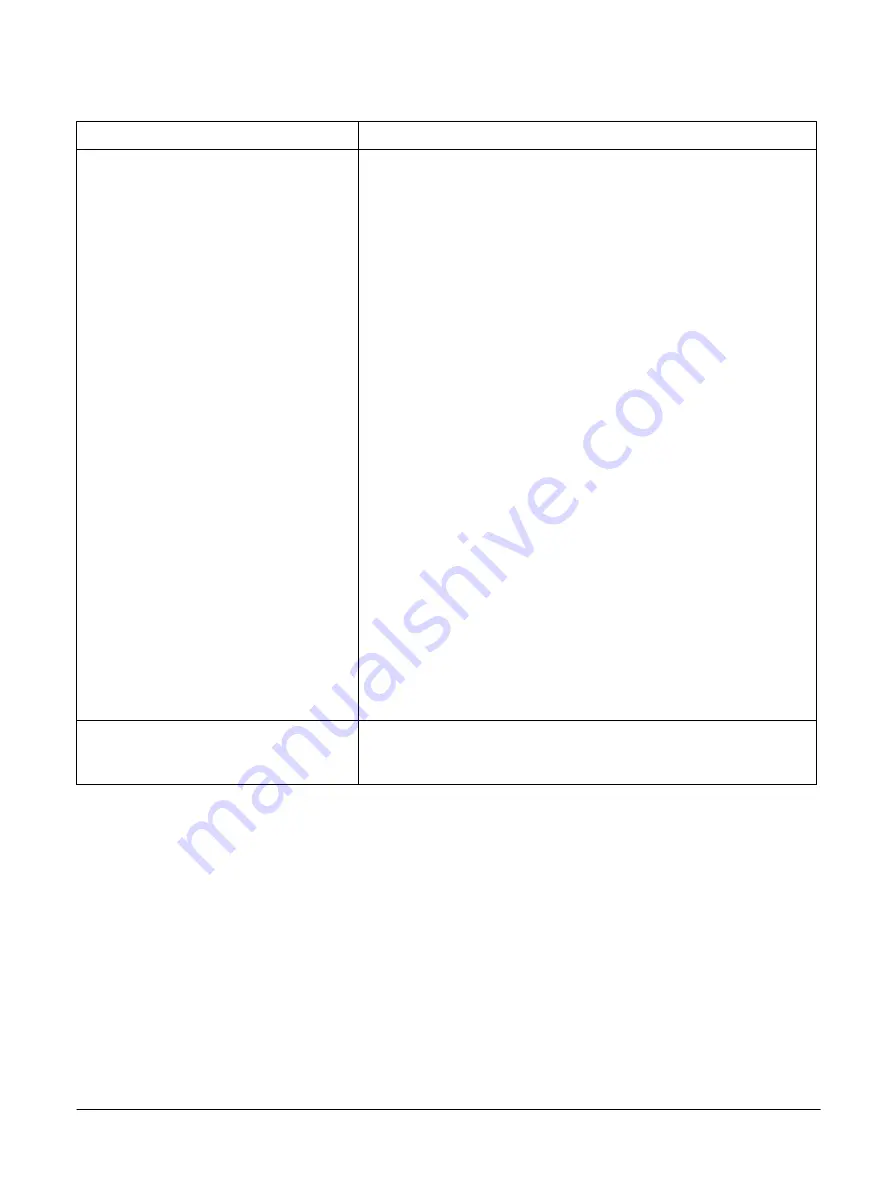

Table A-1 Armv8 Debug UNPREDICTABLE behaviors (continued)

Scenario

Behavior

Accessing reserved debug registers

The core deviates from preferred behavior because the hardware cost to decode

some of these addresses in debug power domain is significantly high.

The actual behavior is:

1. For reserved debug registers in the address range

0x000

-

0xCFC

and

Performance Monitors registers in the address range

0x000

, the response is

either

CONSTRAINED UNPREDICTABLE

Error or

RES0

when any of the following

errors occurs:

Off

The core power domain is either completely off or in a low-power

state where the core power domain registers cannot be accessed.

DLK

DoubleLockStatus()

is TRUE and OS double-lock is locked

(EDPRSR.DLK is 1).

OSLK

OS lock is locked (OSLSR_EL1.OSLK is 1).

2. For reserved debug registers in the address ranges

0x400

-

0x4FC

and

0x800

-

0x8FC

, the response is

CONSTRAINED UNPREDICTABLE

Error or

RES0

do not apply and the following error occurs:

EDAD

AllowExternalDebugAccess()

is FALSE. External debug

access is disabled.

3. For reserved Performance Monitor registers in the address ranges

0x000

-

0x0FC

and

0x400

-

0x47C

, the response is either

CONSTRAINED

UNPREDICTABLE

Error, or

RES0

when the conditions in

and

do not apply,

and the following error occurs:

EPMAD

AllowExternalPMUAccess()

is FALSE. External Performance

Monitors access is disabled.

Clearing the

clear-after-read

EDPRSR bits when

Core power domain is on, and

DoubleLockStatus()

is TRUE

The core behaves as indicated in the sole Preference:

•

Bits are not cleared to zero.

A Cortex

®

-A76 Core AArch32 unpredictable behaviors

A.3 Armv8 Debug UNPREDICTABLE behaviors

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

Appx-A-596

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......