D9.73

TRCVIIECTLR, ViewInst Include-Exclude Control Register

The TRCVIIECTLR defines the address range comparators that control the ViewInst Include/Exclude

control.

Bit field descriptions

The TRCVIIECTLR is a 32-bit register.

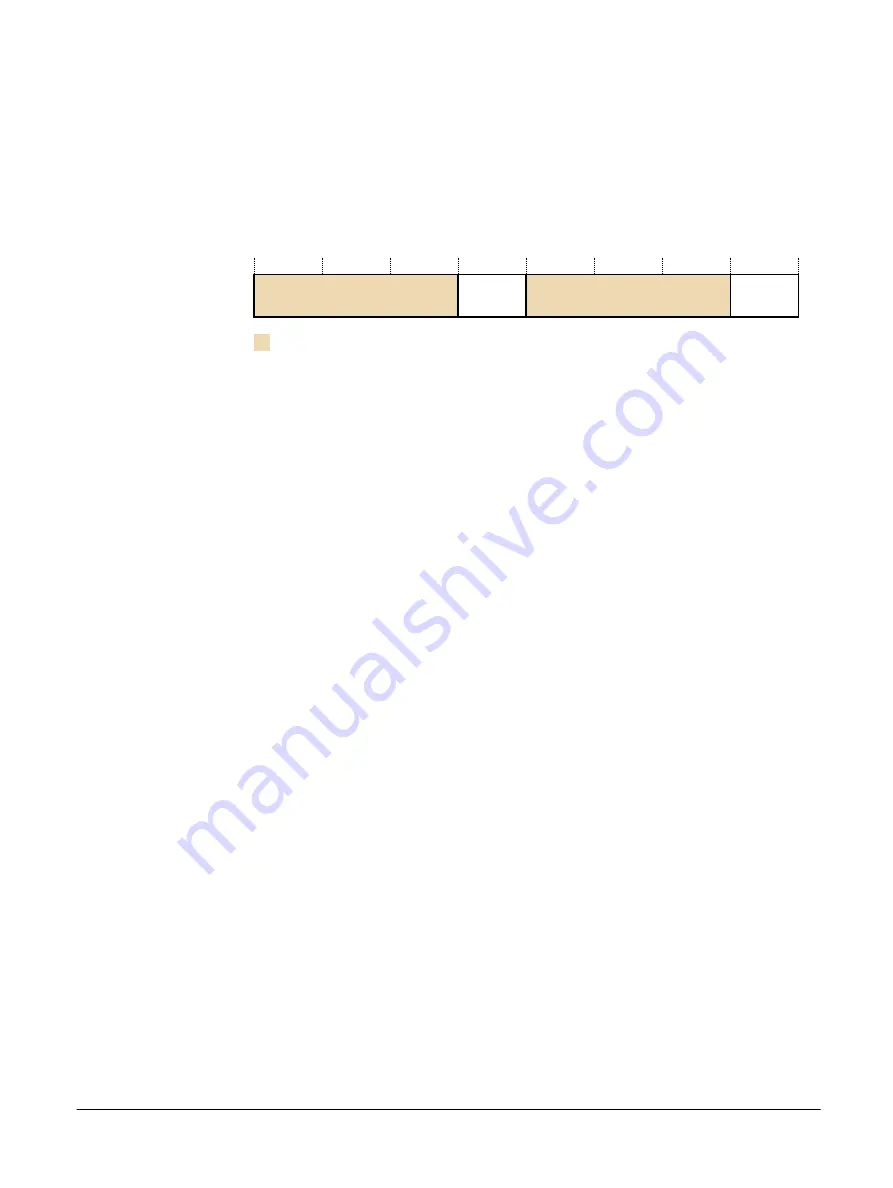

31

0

EXCLUDE

16 15

INCLUDE

19

20

3

4

RES

0

Figure D9-70 TRCVIIECTLR bit assignments

RES0, [31:20]

RES0

Reserved.

EXCLUDE, [19:16]

Defines the address range comparators for ViewInst exclude control. One bit is provided for

each implemented Address Range Comparator.

RES0, [15:4]

RES0

Reserved.

INCLUDE, [3:0]

Defines the address range comparators for ViewInst include control.

Selecting no include comparators indicates that all instructions must be included. The exclude

control indicates which ranges must be excluded.

One bit is provided for each implemented Address Range Comparator.

Bit fields and details not provided in this description are architecturally defined. See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture profile

.

The TRCVIIECTLR can be accessed through the external debug interface, offset

0x084

.

D9 ETM registers

D9.73 TRCVIIECTLR, ViewInst Include-Exclude Control Register

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D9-585

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......