Usage constraints

Accessing the CPUECTLR_EL1

The CPU Extended Control Register can be written only when the system is idle. Arm

recommends that you write to this register after a powerup reset, before the MMU is enabled.

This register can be read using MRS with the following syntax:

MRS <Xt>,<systemreg>

This register can be written using MSR with the following syntax:

MSR <systemreg>, <Xt>

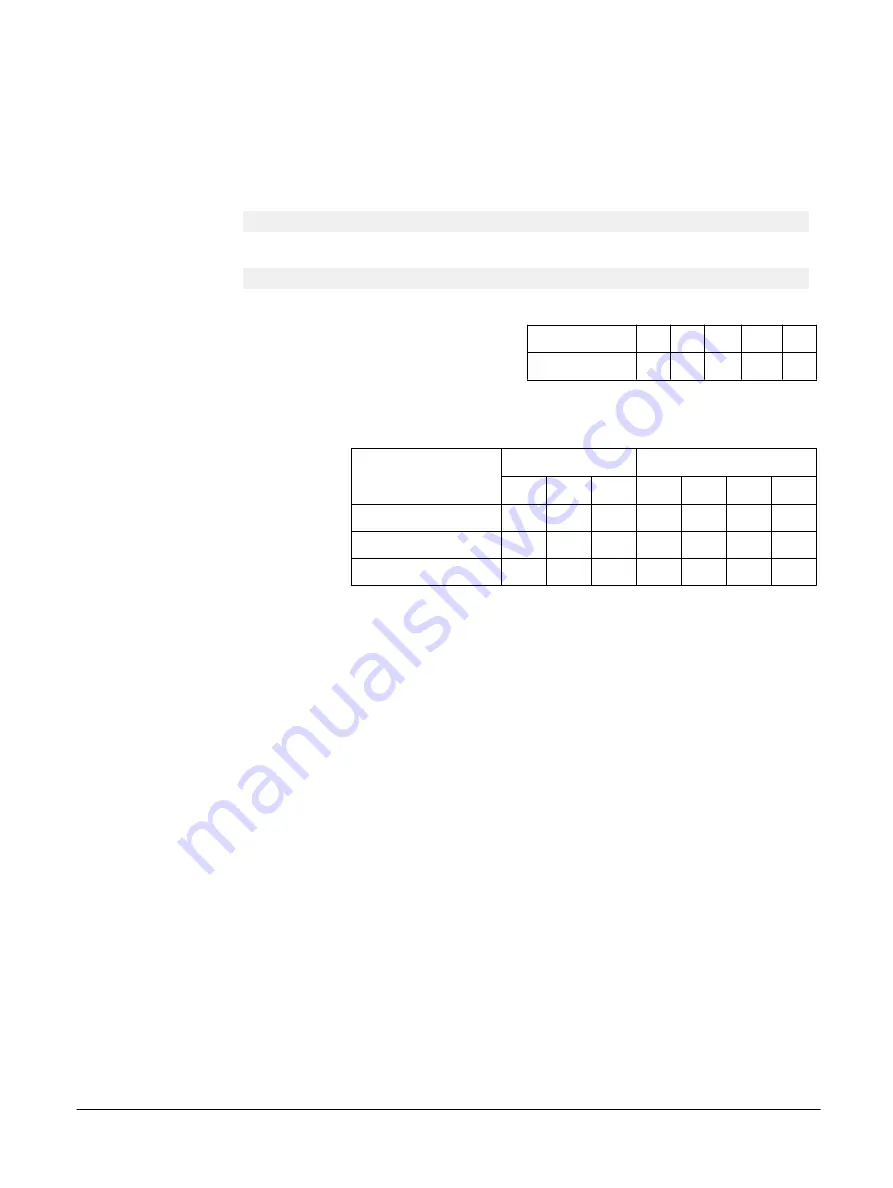

This syntax is encoded with the following settings in the instruction encoding:

<systemreg>

op0 op1 CRn CRm op2

CPUECTLR_EL1 11

000 1111 0001 100

Accessibility

This register is accessible in software as follows:

<systemreg>

Control

Accessibility

E2H

TGE

NS

EL0

EL1

EL2

EL3

CPUECTLR_EL1

x

x

0

-

RW

n/a

RW

CPUECTLR_EL1

x

0

1

-

RW

RW

RW

CPUECTLR_EL1

x

1

1

-

n/a

RW

RW

'n/a' Not accessible. The PE cannot be executing at this Exception level, so this access is not possible.

Traps and enables

For a description of the prioritization of any generated exceptions, see

Synchronous exception

prioritization

in the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture

profile

for exceptions taken to AArch64 state.

Access to this register depends on bit[1] of ACTLR_EL2 and ACTLR_EL3.

B2 AArch64 system registers

B2.26 CPUECTLR_EL1, CPU Extended Control Register, EL1

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B2-179

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......