B2.47

ESR_EL1, Exception Syndrome Register, EL1

The ESR_EL1 holds syndrome information for an exception taken to EL1.

Bit field descriptions

ESR_EL1 is a 32-bit register, and is part of the Exception and fault handling registers functional group.

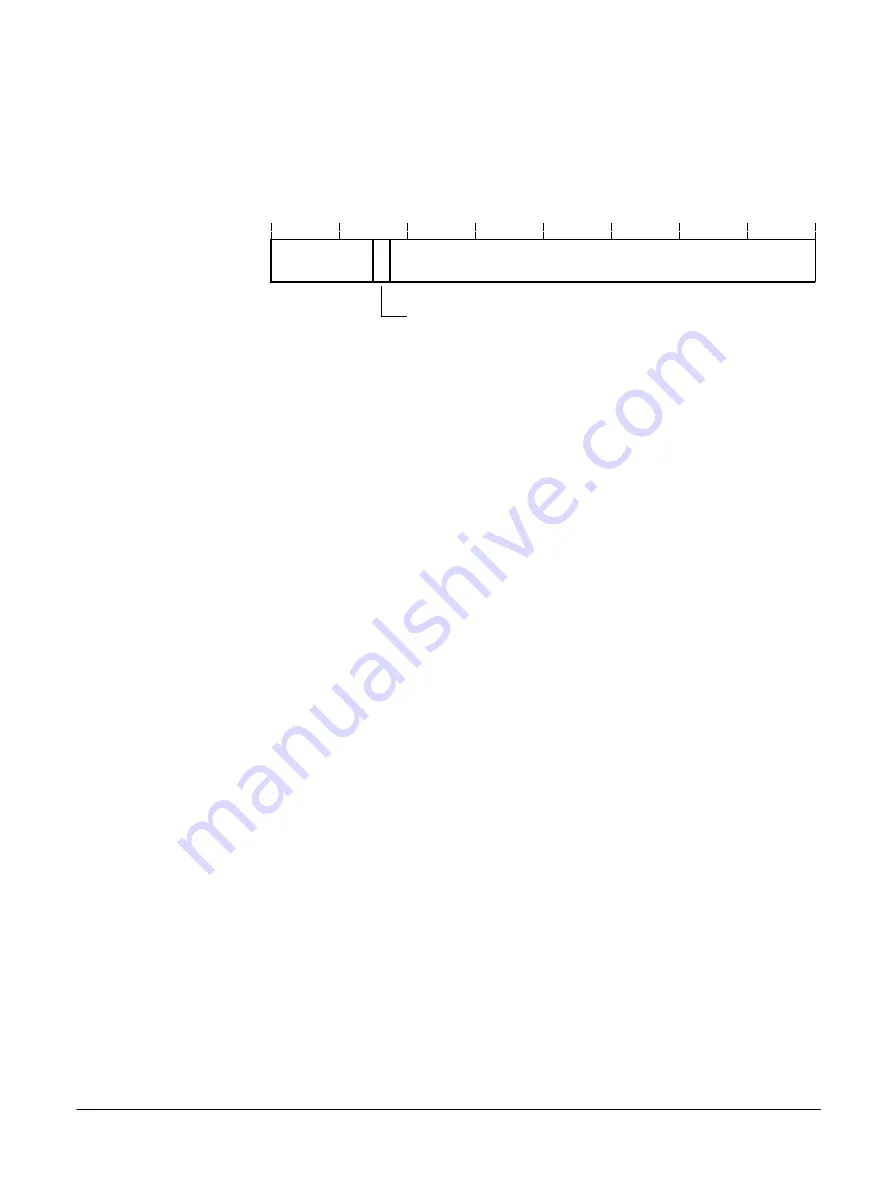

31

0

ISS

IL

EC

25 24

26

Figure B2-34 ESR_EL1 bit assignments

EC, [31:26]

Exception Class. Indicates the reason for the exception that this register holds information

about.

IL, [25]

Instruction Length for synchronous exceptions. The possible values are:

0

16-bit.

1

32-bit.

This field is

1

for the SError interrupt, instruction aborts, misaligned PC, Stack pointer

misalignment, data aborts for which the ISV bit is

0

, exceptions caused by an illegal instruction

set state, and exceptions using the

0x00

Exception Class.

ISS, [24:0]

Syndrome information.

When reporting a virtual SEI, bits[24:0] take the value of VSESRL_EL2[24:0].

When reporting a physical SEI, the following occurs:

• IDS==0 (architectural syndrome).

• AET always reports an uncontainable error (UC) with value

0b000

or an unrecoverable error (UEU)

with value

0b001

.

• EA is

RES0

.

When reporting a synchronous data abort, EA is

RES0

.

B2.102 VSESR_EL2, Virtual SError Exception Syndrome Register

Configurations

This register has no configuration options.

B2 AArch64 system registers

B2.47 ESR_EL1, Exception Syndrome Register, EL1

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B2-208

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......