(continued)

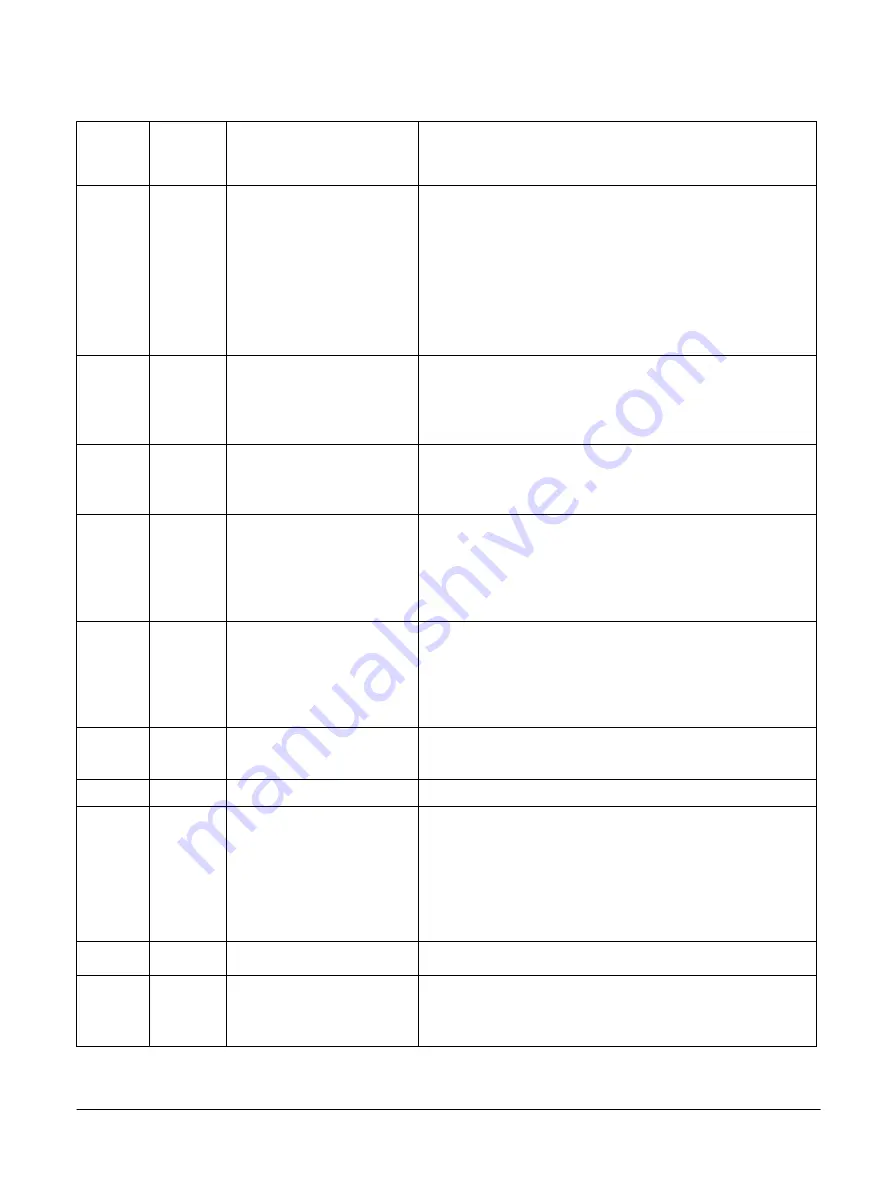

Event

number

PMU

event bus

(to trace)

Event mnemonic

Event description

0x15

[21]

L1D_CACHE_WB

L1 data cache Write-Back. This event counts any write-back of data

from the L1 data cache to L2 or L3. This counts both victim line

evictions and snoops, including cache maintenance operations.

The following instructions are not counted:

•

Invalidations which do not result in data being transferred out of

the L1.

•

Full-line writes which write to L2 without writing L1, such as write

streaming mode.

0x16

[24:22]

L2D_CACHE

L2 data cache access. This event counts any transaction from L1 which

looks up in the L2 cache, and any write-back from the L1 to the L2.

Snoops from outside the core and cache maintenance operations are not

counted.

0x17

[27:25]

L2D_CACHE_REFILL

L2 data cache refill. This event counts any cacheable transaction from

L1 which causes data to be read from outside the core. L2 refills caused

by stashes into L2 should not be counted.

0x18

[30:28]

L2D_CACHE_WB

L2 data cache write-back. This event counts any write-back of data

from the L2 cache to outside the core. This includes snoops to the L2

which return data, regardless of whether they cause an invalidation.

Invalidations from the L2 which do not write data outside of the core

and snoops which return data from the L1 are not counted.

0x19

[32:31]

BUS_ACCESS

Bus access. This event counts for every beat of data transferred over the

data channels between the core and the SCU. If both read and write

data beats are transferred on a given cycle, this event is counted twice

on that cycle. This event counts the sum of BUS_ACCESS_RD and

BUS_ACCESS_WR.

0x1A

[33]

MEMORY_ERROR

Local memory error. This event counts any correctable or uncorrectable

memory error (ECC or parity) in the protected core RAMs.

0x1B

[36:34]

INST_SPEC

Operation speculatively executed

0x1C

[37]

TTBR_WRITE_RETIRED

Instruction architecturally executed, condition code check pass, write to

TTBR.This event only counts writes to TTBR0/TTBR1 in AArch32

state and TTBR0_EL1/TTBR1_EL1 in AArch64 state.

The following instructions are not counted:

•

Accesses to TTBR0_EL12/TTBR1_EL12 or TTBR0_EL2/

TTBR1_EL2.

0x1D

[38]

BUS_CYCLES

Bus cycles. This event duplicates CPU_CYCLES.

0x1E

[39]

CHAIN

For odd-numbered counters, increments the count by one for each

overflow of the preceding even-numbered counter. For even-numbered

counters, there is no increment.

C2 Performance Monitor Unit

C2.3 PMU events

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

C2-376

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......