B2.93

TCR_EL1, Translation Control Register, EL1

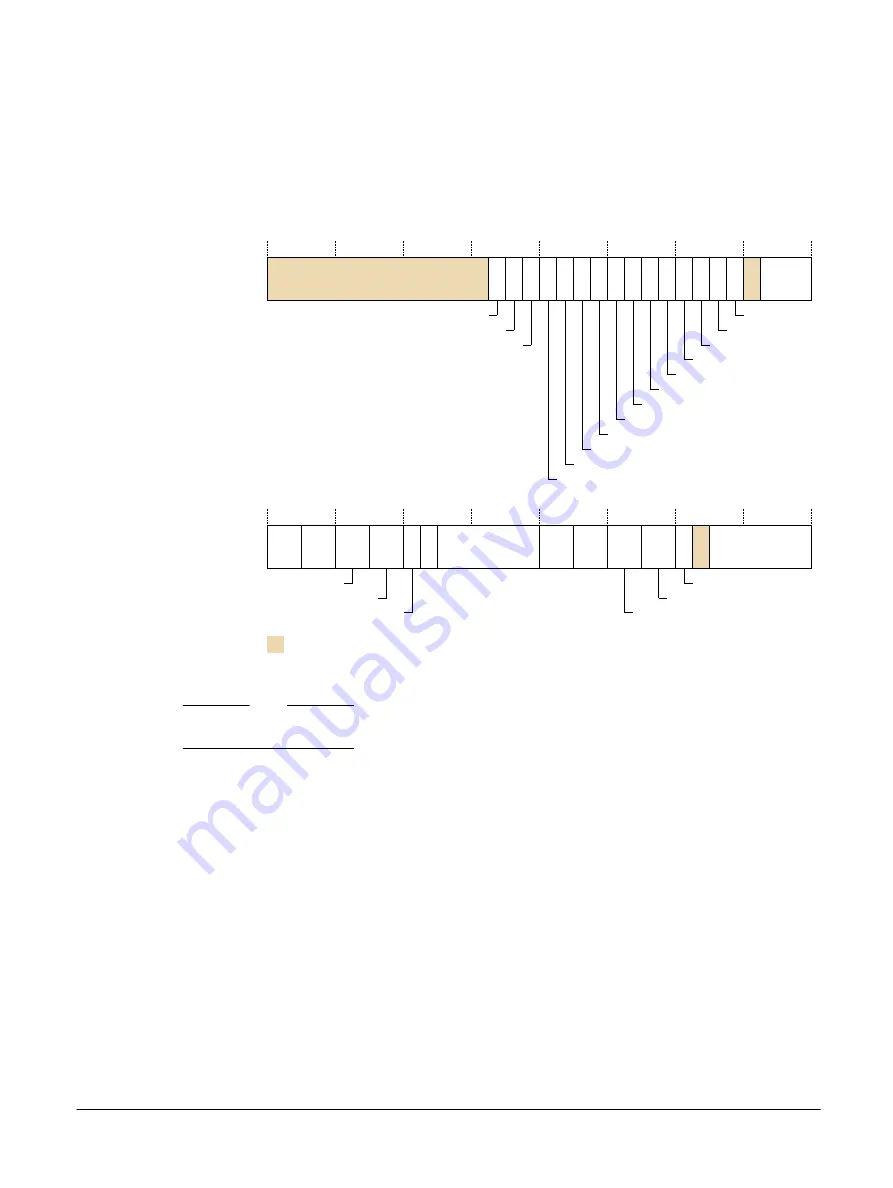

The TCR_EL1 determines which Translation Base registers define the base address register for a

translation table walk required for stage 1 translation of a memory access from EL0 or EL1 and holds

cacheability and shareability information.

Bit field descriptions

TCR_EL1 is a 64-bit register, and is part of the Virtual memory control registers functional group.

63

51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35

IPS

34

32

HWU162

HWU161

HWU160

HWU159

HWU062

HWU061

HWU060

HWU059

HPD1

HPD0

HD

HA

TBI1

TBI0

AS

TG1

31 30

SH1

29 28 27 26 25 24 23

A1

22

T1SZ

21

16

TG0

15 14

SH0

13 12 11 10 9 8 7 6

T0SZ

5

0

ORGN1

IRGN1

EPD

ORGN0

IRGN0

EPD

RES

0

Figure B2-77 TCR_EL1 bit assignments

Note

Bits[50:39], architecturally defined, are implemented in the core.

HD, [40]

Hardware management of dirty state in stage 1 translations from EL0 and EL1. The possible

values are:

0

Stage 1 hardware management of dirty state disabled.

1

Stage 1 hardware management of dirty state enabled, only if the HA bit is also set to 1.

HA, [39]

Hardware Access flag update in stage 1 translations from EL0 and EL1. The possible values are:

0

Stage 1 Access flag update disabled.

1

Stage 1 Access flag update enabled.

Configurations

RW fields in this register reset to

UNKNOWN

values.

Bit fields and details that are not provided in this description are architecturally defined. See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture profile

.

B2 AArch64 system registers

B2.93 TCR_EL1, Translation Control Register, EL1

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B2-278

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......