D9.53

TRCPDSR, Power Down Status Register

The TRCPDSR indicates the power down status of the ETM trace unit.

Bit field descriptions

The TRCPDSR is a 32-bit register.

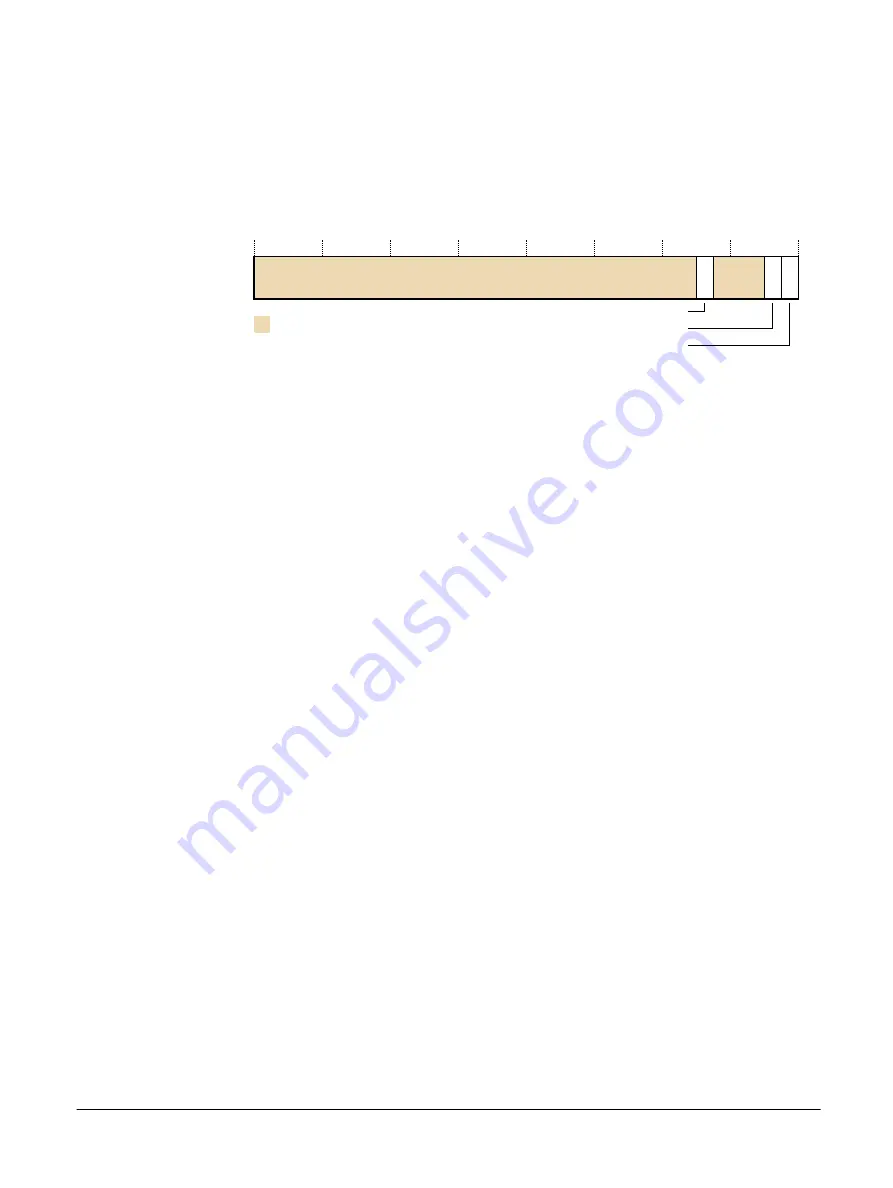

31

6 5 4

2 1 0

OSLK

STICKYPD

POWER

RES

0

Figure D9-51 TRCPDSR bit assignments

RES0, [31:6]

RES0

Reserved.

OSLK, [5]

OS lock status.

0

The OS Lock is unlocked.

1

The OS Lock is locked.

RES0, [4:2]

RES0

Reserved.

STICKYPD, [1]

Sticky power down state.

0

Trace register power has not been removed since the TRCPDSR was last read.

1

Trace register power has been removed since the TRCPDSR was last read.

This bit is set to 1 when power to the ETM trace unit registers is removed, to indicate that

programming state has been lost. It is cleared after a read of the TRCPDSR.

POWER, [0]

Indicates the ETM trace unit is powered:

0

ETM trace unit is not powered. The trace registers are not accessible and they all

return an error response.

1

ETM trace unit is powered. All registers are accessible.

If a system implementation allows the ETM trace unit to be powered off independently of the

debug power domain, the system must handle accesses to the ETM trace unit appropriately.

Bit fields and details not provided in this description are architecturally defined. See the

Arm

®

Architecture Reference Manual Armv8, for Armv8-A architecture profile

.

The TRCPDSR can be accessed through the external debug interface, offset

0x314

.

D9 ETM registers

D9.53 TRCPDSR, Power Down Status Register

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D9-563

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......