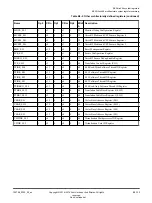

Table B2-1 Registers with implementation defined bit fields (continued)

Name

Op0 CRn Op1 CRm Op2 Width Description

TTBR1_EL2

3

c2

4

c0

1

64

B2.100 TTBR1_EL2, Translation Table Base Register 1, EL2

VDISR_EL2

3

c12

4

c1

1

64

B2.101 VDISR_EL2, Virtual Deferred Interrupt Status Register,

EL2

VSESR_EL2

3

c5

4

c2

3

64

B2.102 VSESR_EL2, Virtual SError Exception Syndrome

Register

VTCR_EL2

3

c2

4

c1

2

32

B2.103 VTCR_EL2, Virtualization Translation Control Register,

EL2

VTTBR_EL2

3

c2

4

c1

0

64

B2.104 VTTBR_EL2, Virtualization Translation Table Base

Register, EL2

Table B2-2 Other architecturally defined registers

Name

Op0

CRn

Op1

CRm

Op2

Widt

h

Description

AFSR0_EL12

3

c5

5

1

0

32

Auxiliary Fault Status Register 0

AFSR1_EL12

3

c5

5

1

1

32

Auxiliary Fault Status Register 1

AMAIR_EL12

3

c10

5

c3

0

64

Auxiliary Memory Attribute Indirection Register

CNTFRQ_EL0

3

c14

3

0

0

32

Counter-timer Frequency register

CNTHCTL_EL2

3

c14

4

c1

0

32

Counter-timer Hypervisor Control register

CNTHP_CTL_EL2

3

c14

4

c2

1

32

Counter-timer Hypervisor Physical Timer Control

register

CNTHP_CVAL_EL2

3

c14

4

c2

2

64

Counter-timer Hyp Physical CompareValue register

CNTHP_TVAL_EL2

3

c14

4

c2

0

32

Counter-timer Hyp Physical Timer TimerValue register

CNTHV_CTL_EL2

3

c14

4

c3

1

32

Counter-timer Virtual Timer Control register

CNTHV_CVAL_EL2

3

c14

4

c3

2

64

Counter-timer Virtual Timer CompareValue register

CNTHV_TVAL_EL2

3

c14

4

c3

0

32

Counter-timer Virtual Timer TimerValue register

CNTKCTL_EL1

3

c14

0

c1

0

32

Counter-timer Kernel Control register

CNTKCTL_EL12

3

c14

5

c1

0

32

Counter-timer Kernel Control register

CNTP_CTL_EL0

3

c14

3

c2

1

32

Counter-timer Physical Timer Control register

CNTP_CTL_EL02

3

c14

5

c2

1

32

Counter-timer Physical Timer Control register

CNTP_CVAL_EL0

3

c14

3

c2

2

64

Counter-timer Physical Timer CompareValue register

CNTP_CVAL_EL02

3

c14

5

c2

2

64

Counter-timer Physical Timer CompareValue register

CNTP_TVAL_EL0

3

c14

3

c2

0

32

Counter-timer Physical Timer TimerValue register

CNTP_TVAL_EL02

3

c14

5

c2

0

32

Counter-timer Physical Timer TimerValue register

CNTPCT_EL0

3

c14

3

c0

1

64

Counter-timer Physical Count register

CNTPS_CTL_EL1

3

c14

7

c2

1

32

Counter-timer Physical Secure Timer Control register

CNTPS_CVAL_EL1

3

c14

7

c2

2

64

Counter-timer Physical Secure Timer CompareValue

register

B2 AArch64 system registers

B2.2 AArch64 architectural system register summary

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

B2-131

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......