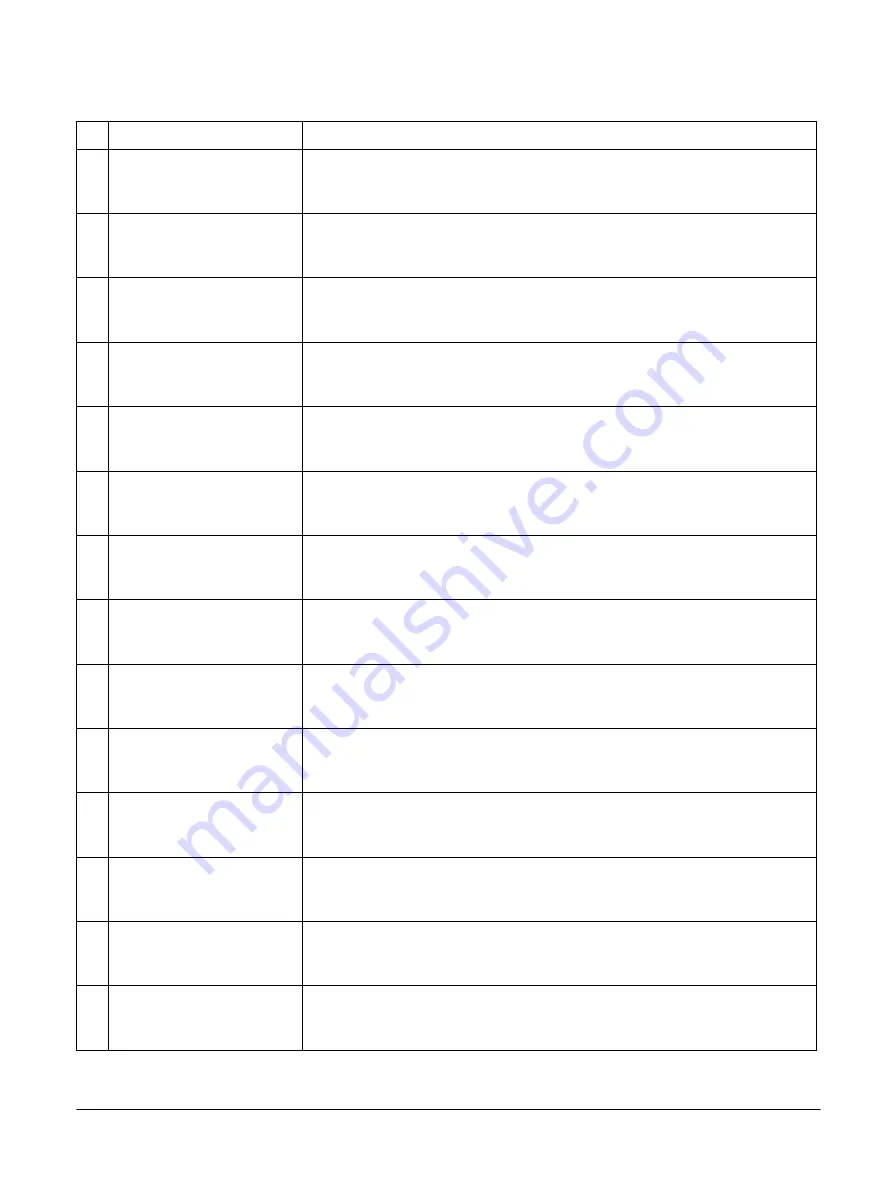

Table D4-2 PMU events (continued)

Bit Event mnemonic

Description

[23] L2D_CACHE_REFILL

L2 Data cache refill:

1

This event is implemented.

[22] L2D_CACHE

L2 Data cache access:

1

This event is implemented.

[21] L1D_CACHE_WB

L1 Data cache Write-Back:

1

This event is implemented.

[20] L1I_CACHE

L1 Instruction cache access:

1

This event is implemented.

[19] MEM_ACCESS

Data memory access:

1

This event is implemented.

[18] BR_PRED

Predictable branch speculatively executed:

1

This event is implemented.

[17] CPU_CYCLES

Cycle:

1

This event is implemented.

[16] BR_MIS_PRED

Mispredicted or not predicted branch speculatively executed:

1

This event is implemented.

[15] UNALIGNED_LDST_RETIRED Instruction architecturally executed, condition check pass - unaligned load or store:

0

This event is not implemented.

[14] BR_RETURN_RETIRED

Instruction architecturally executed, condition check pass - procedure return:

0

This event is not implemented.

[13] BR_IMMED_RETIRED

Instruction architecturally executed - immediate branch:

0

This event is not implemented.

[12] PC_WRITE_RETIRED

Instruction architecturally executed, condition check pass - software change of the PC:

0

This event is not implemented.

[11] CID_WRITE_RETIRED

Instruction architecturally executed, condition check pass - write to CONTEXTIDR:

1

This event is implemented.

[10] EXC_RETURN

Instruction architecturally executed, condition check pass - exception return:

1

This event is implemented.

D4 AArch32 PMU registers

D4.2 PMCEID0, Performance Monitors Common Event Identification Register 0

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D4-437

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......