D9.1

ETM register summary

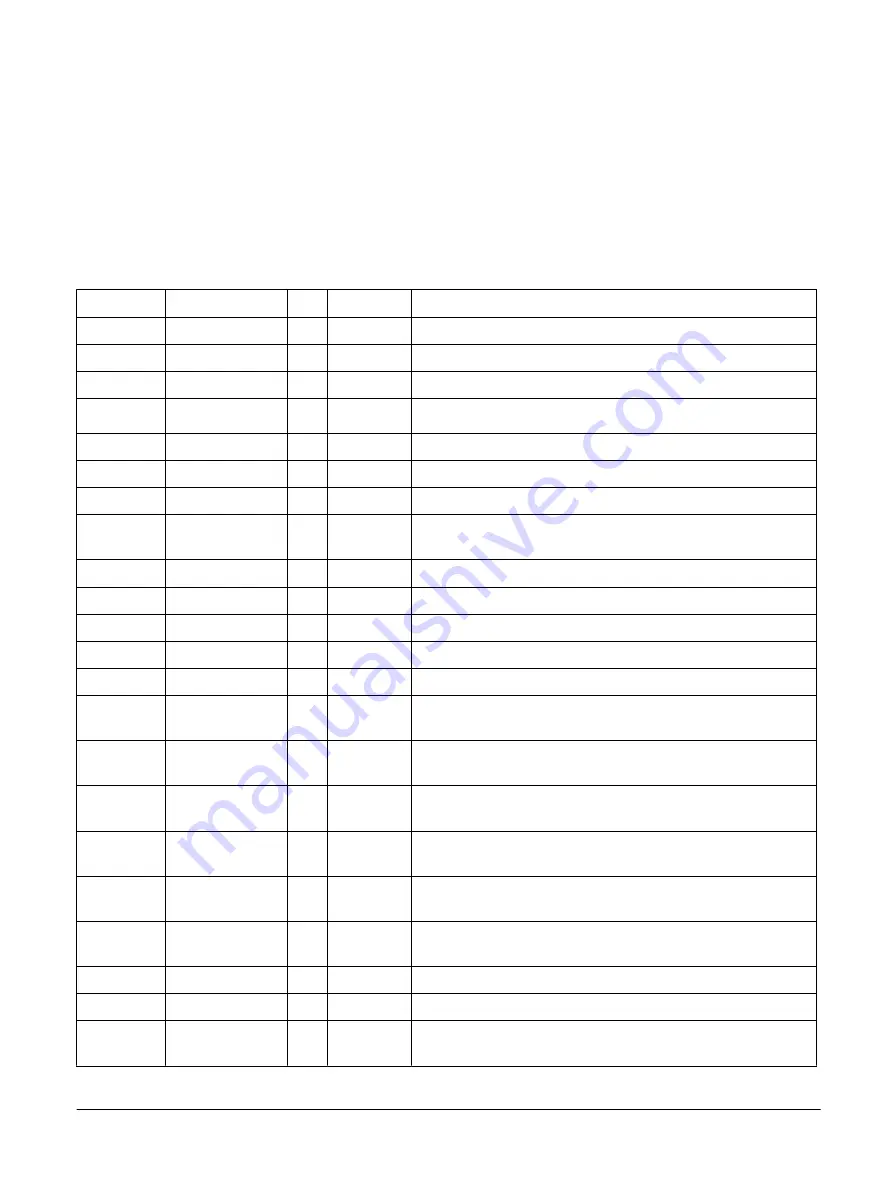

This section summarizes the ETM trace unit registers.

All ETM trace unit registers are 32-bit wide. The description of each register includes its offset from a

base address. The base address is defined by the system integrator when placing the ETM trace unit in

the Debug-APB memory map.

The following table lists all of the ETM trace unit registers.

Table D9-1 ETM trace unit register summary

Offset

Name

Type Reset

Description

0x004

TRCPRGCTLR

RW

0x00000000

D9.60 TRCPRGCTLR, Programming Control Register

0x00C

TRCSTATR

RO

0x00000003

D9.68 TRCSTATR, Status Register

0x010

TRCCONFIGR

RW

UNK

D9.20 TRCCONFIGR, Trace Configuration Register

0x018

TRCAUXCTLR

RW

0x00000000

D9.5 TRCAUXCTLR, Auxiliary Control Register

0x020

TRCEVENTCTL0R RW

UNK

D9.26 TRCEVENTCTL0R, Event Control 0 Register

0x024

TRCEVENTCTL1R RW

UNK

D9.27 TRCEVENTCTL1R, Event Control 1 Register

0x02C

TRCSTALLCTLR

RW

UNK

D9.67 TRCSTALLCTLR, Stall Control Register

0x030

TRCTSCTLR

RW

UNK

D9.71 TRCTSCTLR, Global Timestamp Control Register

0x034

TRCSYNCPR

RW

UNK

D9.69 TRCSYNCPR, Synchronization Period Register

0x038

TRCCCCTLR

RW

UNK

D9.7 TRCCCCTLR, Cycle Count Control Register

0x03C

TRCBBCTLR

RW

UNK

D9.6 TRCBBCTLR, Branch Broadcast Control Register

0x040

TRCTRACEIDR

RW

UNK

D9.70 TRCTRACEIDR, Trace ID Register

0x080

TRCVICTLR

RW

UNK

D9.72 TRCVICTLR, ViewInst Main Control Register

0x084

TRCVIIECTLR

RW

UNK

D9.73 TRCVIIECTLR, ViewInst Include-Exclude Control Register

0x088

TRCVISSCTLR

RW

UNK

D9.74 TRCVISSCTLR, ViewInst Start-Stop Control Register

0x100

TRCSEQEVR0

RW

UNK

D9.62 TRCSEQEVRn, Sequencer State Transition Control Registers 0-2

0x104

TRCSEQEVR1

RW

UNK

D9.62 TRCSEQEVRn, Sequencer State Transition Control Registers 0-2

0x108

TRCSEQEVR2

RW

UNK

D9.62 TRCSEQEVRn, Sequencer State Transition Control Registers 0-2

0x118

TRCSEQRSTEVR

RW

UNK

D9.63 TRCSEQRSTEVR, Sequencer Reset Control Register

0x11C

TRCSEQSTR

RW

UNK

D9.64 TRCSEQSTR, Sequencer State Register

0x120

TRCEXTINSELR

RW

UNK

D9.28 TRCEXTINSELR, External Input Select Register

0x140

TRCCNTRLDVR0

RW

UNK

D9.18 TRCCNTRLDVRn, Counter Reload Value Registers 0-1

D9 ETM registers

D9.1 ETM register summary

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

D9-495

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......