A5.2

TLB organization

The TLB is a cache of recently executed page translations within the MMU. The Cortex-A76 core

implements a two-level TLB structure. The TLB stores all page sizes and is responsible for breaking

these down in to smaller pages when required for the data or instruction L1 TLB.

A5.2.1

Instruction L1 TLB

The instruction L1 TLB is implemented as a 48-entry fully associative structure. This TLB caches entries

at the 4KB, 16KB, 64KB, 2MB, and 32MB granularity of VA to PA mapping only.

A hit in the instruction L1 TLB provides a single

CLK

cycle access to the translation, and returns the PA

to the instruction cache for comparison. It also checks the access permissions to signal an Instruction

Abort.

A5.2.2

Data L1 TLB

The data L1 TLB is a 48-entry fully associative TLB that is used by load and store operations. The cache

entries have 4KB, 16KB, 64KB, 2MB, and 512MB granularity of VA to PA mappings only.

A hit in the data L1 TLB provides a single

CLK

cycle access to the translation, and returns the PA to the

data cache for comparison. It also checks the access permissions to signal a Data Abort.

A5.2.3

L2 TLB

The L2 TLB structure is shared by instruction and data. It handles misses from the instruction and data

L1 TLBs.

The following table describes the characteristic that applies to the L2 TLB.

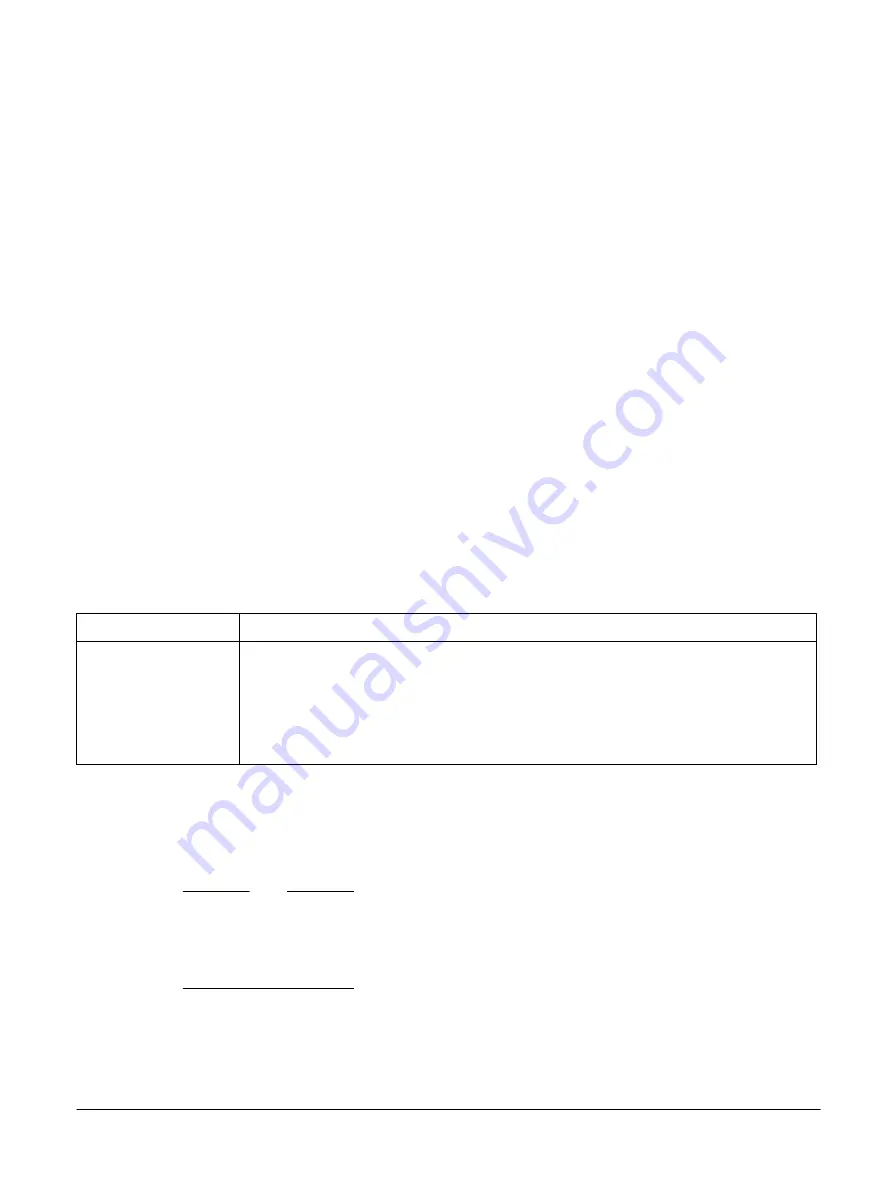

Table A5-3 Characteristic of the L2 TLB

Characteristic

Note

5-way, set associative,

1280-entry cache

Stores:

•

VA to PA mappings for 4KB, 16KB, 64KB, 2MB, 32MB, 512MB, and 1GB block sizes.

•

Intermediate physical address

(IPA) to PA mappings for 2MB and 1GB (in a 4KB translation

granule), 32MB (in a 16K translation granule), and 512MB (in a 64K granule) block sizes. Only

Non-secure EL1 and EL0 stage 2 translations are cached.

•

Intermediate PAs obtained during a translation table walk.

Access to the L2 TLB usually takes three cycles. If a different page or block size mapping is used, then

access to the L2 TLB can take longer.

The L2 TLB supports four translation table walks in parallel (four TLB misses), and can service two

TLB lookups while the translation table walks are in progress. If there are six successive misses, the L2

TLB will stall.

Note

The main TLB is invalidated automatically at reset unless the DISCACHEINVLD signal is set HIGH

when the Cortex-A76 core is reset. This signal must only be used in diagnostic mode. If caches are not

invalidated on reset, their functionality cannot be guaranteed. See the

Arm

®

DynamIQ

™

Shared Unit

Technical Reference Manual

for more information on DISCACHEINVLD.

A5 Memory Management Unit

A5.2 TLB organization

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

A5-64

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......