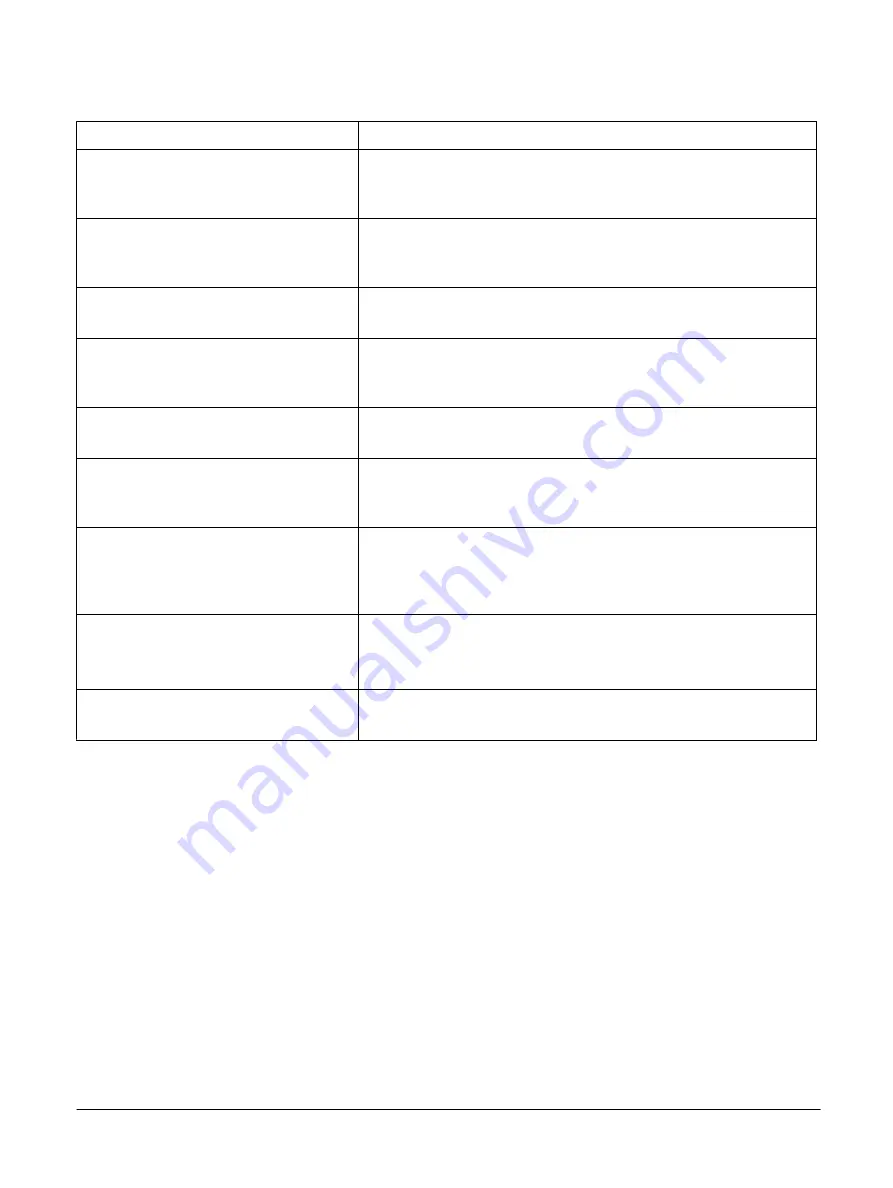

Table A-1 Armv8 Debug UNPREDICTABLE behaviors (continued)

Scenario

Behavior

P ≥ M and P ≠ 31: reads and writes of PM

XEVTYPER_EL0 and PMXEVCNTR_EL0

The core implements:

•

A simple implementation where all of SEL[4:0] are implemented, and if P ≥

M and P ≠ 31 then the register is

RES0

.

P ≥ M and P ≠ 31: value read in

PMSELR_EL0.SEL

The core implements:

•

A simple implementation where all of SEL[4:0] are implemented, and if P ≥

M and P ≠ 31 then the register is

RES0

.

P = 31: reads and writes of PMXEVCNTR_EL0

The core implements:

•

RES0

.

n ≥ M: Direct access to PMEVCNTRn_EL0 and

PMEVTYPERn_EL0

The core implements:

•

If n ≥ N, then the instruction is

UNALLOCATED

.

•

Otherwise if n ≥ M, then the register is

RES0

.

Exiting Debug state while instruction issued

through EDITR is in flight

The core implements the following option:

•

The instruction completes in Debug state before executing the restart.

Using memory-access mode with a non-word-

aligned address

The core behaves as indicated in the sole Preference:

•

Does unaligned accesses, faulting if these are not permitted for the memory

type.

Access to memory-mapped registers mapped to

Normal memory

The core behaves as indicated in the sole Preference:

•

The access is generated, and accesses might be repeated, gathered, split or

resized, in accordance with the rules for Normal memory, meaning the effect is

UNPREDICTABLE

.

Not word-sized accesses or (AArch64 only)

doubleword-sized accesses

>

The core behaves as indicated in the sole Preference:

•

Reads occur and return

UNKNOWN

data.

•

Writes set the accessed register(s) to

UNKNOWN

.

External debug write to register that is being reset The core behaves as indicated in the sole Preference:

•

Takes reset value.

A Cortex

®

-A76 Core AArch32 unpredictable behaviors

A.3 Armv8 Debug UNPREDICTABLE behaviors

100798_0300_00_en

Copyright © 2016–2018 Arm Limited or its affiliates. All rights

reserved.

Appx-A-595

Non-Confidential

Summary of Contents for Cortex-A76 Core

Page 4: ......

Page 22: ......

Page 23: ...Part A Functional description ...

Page 24: ......

Page 119: ...Part B Register descriptions ...

Page 120: ......

Page 363: ...Part C Debug descriptions ...

Page 364: ......

Page 401: ...Part D Debug registers ...

Page 402: ......

Page 589: ...Part E Appendices ...

Page 590: ......