Chapter 4. Configuration Registers

4-1

Chapter 4

Configuration Registers

This chapter describes the programmable configuration registers of the MPC8240. These

registers are generally set up by initialization software following a power-on reset, hard

reset, or error handling routines. All the configuration registers of the MPC8240 are

intrinsically little-endian. In the register descriptions of this chapter, bit 0 is the least

significant bit of the register. This bit numbering is based upon the PCI standard for register

bit order numbering and is opposite from the standard PowerPC bit ordering where bit b0

is the most significant bit of the register.

Reserved bits in the register descriptions are not guaranteed to have predictable values.

Software must preserve the values of reserved bits when writing to a configuration register.

Also, when reading from a configuration register, software should not rely on the value of

any reserved bit remaining consistent. Thus, the values of reserved bit positions must first

be read, merged with the new values for other bit positions, and then written back. Software

should use the transfer size shown in the register bit descriptions throughout this chapter.

4.1 Configuration Register Access

The MPC8240 configuration registers are accessible from the processor core through

memory-mapped configuration ports. The registers are accessed by an indirect method

similar to accessing PCI device configuration registers. A 32-bit register address

0x8000_00nn, where nn is the address offset of the desired configuration register (see

Table 4-2 and Figure 4-1), is written to the CONFIG_ADDR port. Then, the data is

accessed at the CONFIG_DAT port. The locations of these ports are described in Table 4-1.

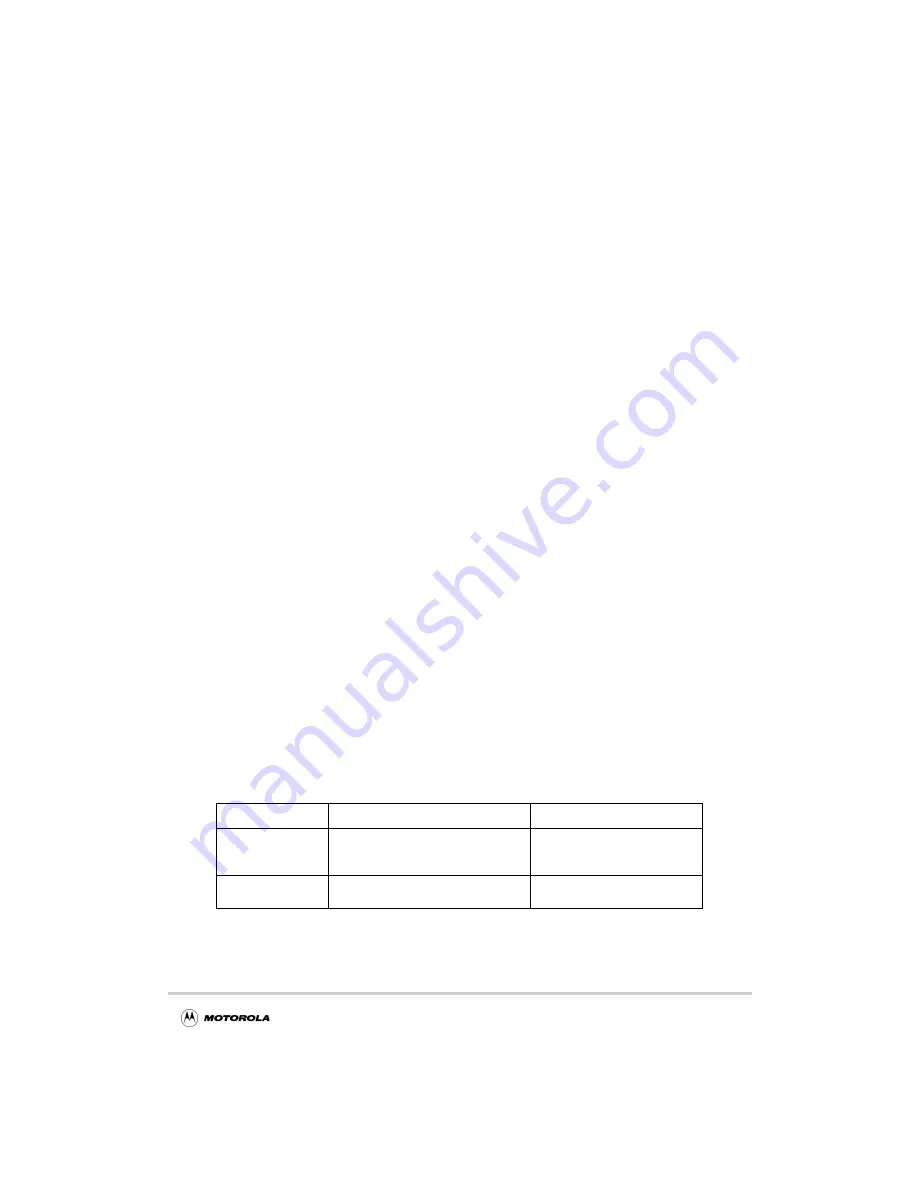

Table 4-1. Internal Register Access Port Locations

Address Map

CONFIG_ADDR

CONFIG_DAT

A

0x8000_0CF8

0x8000_0CFC–0x8000_0CFF

B

Any word-aligned address within the

range 0xFEC0_0000–0xFEDF_FFFC

*

0xFEE0_0000–0xFEEF_FFFF

1

1

Every word within this range is aliased to the same location

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...