Chapter 8. DMA Controller

8-3

DMA Operation

8.3 DMA Operation

The DMA controller operates in two modes—direct and chaining. In direct mode, the

software is responsible for initializing the source address register (SAR), destination

address register (DAR), and byte count register (BCR). In chaining mode, the software

must first build descriptors segments in local or remote memory. Then the current

descriptor address register (CDAR) is initialized to point to the first descriptor in memory.

In both modes, setting the channel start bit in the DMA mode register (DMR) starts the

DMA transfer.

The DMA controller supports misaligned transfers for both the source and destination

addresses. It gathers data beginning at the source address and aligns it accordingly before

sending it to the destination address. The DMA controller assumes that the source and

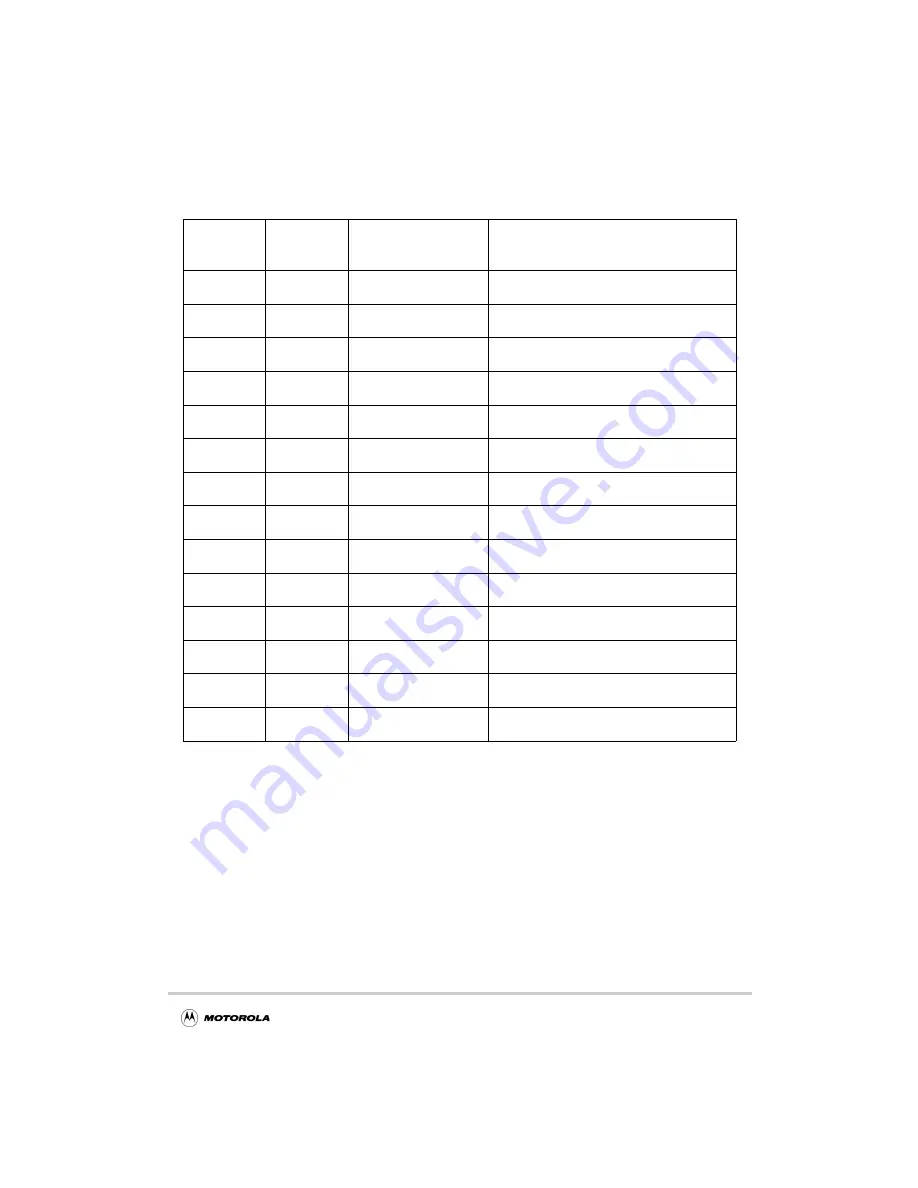

Table 8-1. DMA Register Summary

PCI Memory

Offset

Local

Memory

Offset

Register Name

Description

0x100

0x0_1100

DMA 0 mode register

(DMR)

Allows software to setup up different DMA modes

and interrupt enables

0x104

0x0_1104

DMA 0 status register

(DSR)

Tracks DMA processes and errors

0x108

0x0_1108

DMA 0 current descriptor

address register (CDAR)

Contains the location of the current descriptor to

be loaded

0x110

0x0_1110

DMA 0 source address

register (SAR)

Contains the source address from which data will

be read

0x118

0x0_1118

DMA 0 destination address

register (DAR)

Contains the destination address to which data

will be written

0x120

0x0_1120

DMA 0 byte count register

(BCR)

Contains the number of bytes to transfer

0x124

0x0_1124

DMA 0 next descriptor

address register (NDAR)

Contains the next descriptor address

0x200

0x0_1200

DMA 1 mode register

(DMR)

Allows software to setup up different DMA modes

and interrupt enables

0x204

0x0_1204

DMA 1 status register

(DSR)

Tracks DMA processes and errors

0x208

0x0_1208

DMA 1 current descriptor

address register (CDAR)

Contains the location of the current descriptor to

be loaded

0x210

0x0_1210

DMA 1 source address

register (SAR)

Contains the source address from which data will

be read

0x218

0x0_1218

DMA 1 destination address

register (DAR)

Contains the destination address to which data

will be written

0x220

0x0_1220

DMA 1 byte count register

(BCR)

Contains the number of bytes to transfer

0x224

0x0_1224

DMA 1 next descriptor

address register (NDAR)

Contains the next descriptor address

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...