Chapter 8. DMA Controller

8-19

DMA Register Descriptions

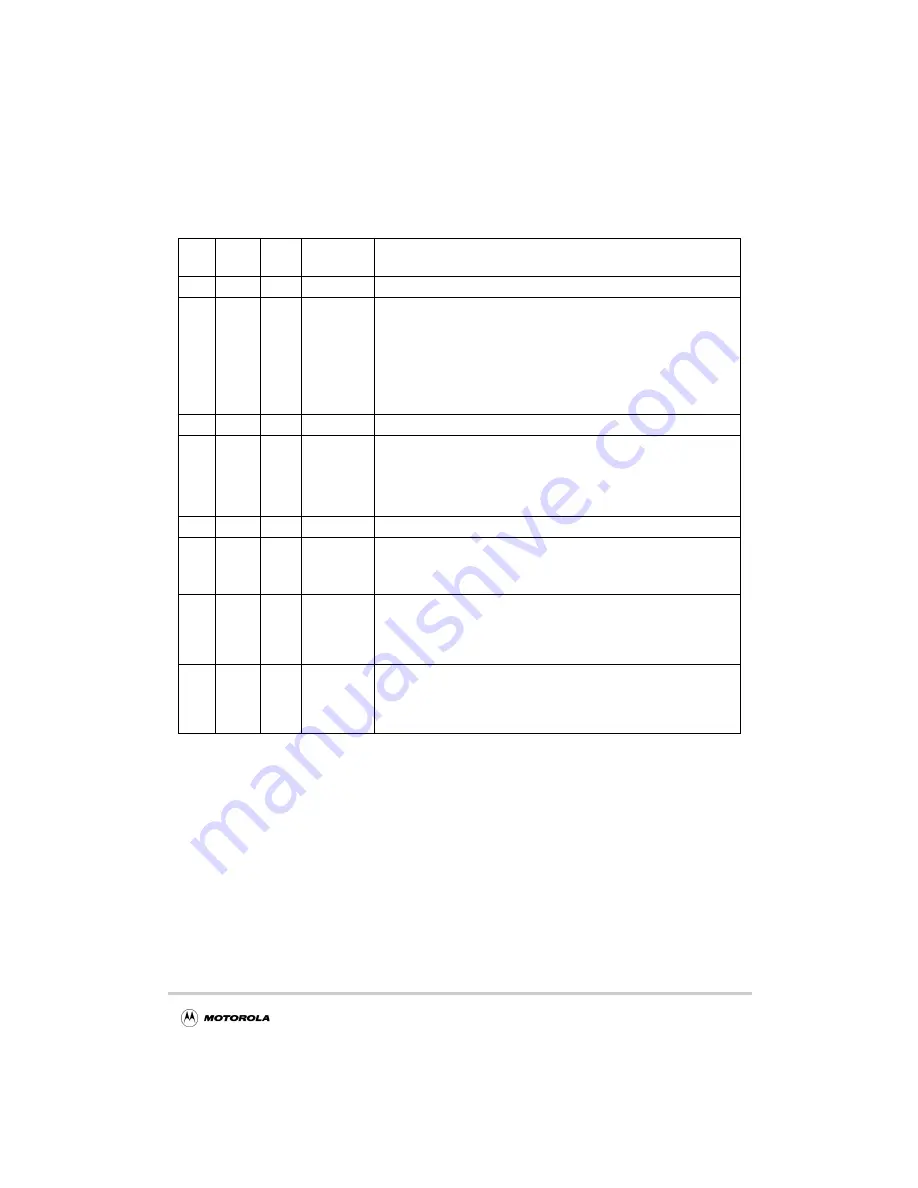

Table 8-4 describes the bit settings for the DSRs.

8.7.3 Current Descriptor Address Registers (CDARs)

The CDARs contains the current address of the descriptor in memory to be loaded, one for

each DMA channel. In chaining mode, software must initialize this register to point to the

first descriptor in memory.

After transferring data defined by the first descriptor, if the EOTD bit in the next descriptor

address register (NDAR) is not set, the DMA controller loads the contents of the NDAR

into the CDAR and begins transferring data based on the next descriptor in memory. If the

NDAR[EOTD] = 1, then the DMA transfer is finished. The SNEN, EOSIE, and CTT bits

are used in both chaining and direct modes. In agent mode, if the descriptor is located in

PCI space (DMR[DL] = 1) and the CDA is within the outbound translation window, then

the CDA is translated. See Section 3.3.2, “Outbound PCI Address Translation,” for more

information.

Table 8-4. DSR Field Descriptions—Offsets 0x104, 0x204

Bits

Name

Reset

Value

R/W

Description

31–8

—

All 0s

R

Reserved

7

LME

0

R/W

Write1 clears

Local memory error

0 No local memory error. When this bit is set, it can only be cleared by

writing a 1 to it or by a hard reset.

1 A memory error condition occurred during the DMA transfer. This bit

mirrors the ErrDR1bits 2, 3, 5. and 6 (see Section 4.8.2, “Error Enabling

and Detection Registers.”) Software should set the corresponding enable

bits in the error enabling register. When an error is detected, software

should clear both the LME bit and the bits in the error detection register. If

DMR[EIE] = 1, an interrupt is generated.

6–5

—

00

R

Reserved

4

PE

0

R/W

Write1 clears

PCI error

0 No PCI error. When this bit is set, it can only be cleared by writing a 1 to it

or by a hard reset.

1 A master or target abort condition or a read parity error occurred on the

PCI bus during the DMA transfer. If DMR[EIE] = 1, an interrupt is

generated.

3

—

0

R

Reserved

2

CB

0

R

Channel busy

0 Channel not busy. This bit is cleared by the MPC8240 as a result of an

error or when the DMA transfer is finished.

1 A DMA transfer is currently in progress.

1

EOSI

0

R/W

Write1 clears

End-of-segment interrupt

0 No end-of-segment condition. When this bit is set, it can only be cleared

by writing a 1 to it or by a hard reset.

1 If CDAR[EOSIE] = 1 and the block of data has finished transferring, this

bit is set and an interrupt is generated.

0

EOCAI

0

R/W

Write1 clears

End-of-chain/direct interrupt

0 DMA transfer not finished. When this bit is set, it can only be cleared by

writing a 1 to it or by a hard reset.

1 If DMR[EOTIE] = 1 and the last DMA transfer is finished, either in

chaining or direct mode, this bit is set and an interrupt is generated.

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...