Chapter 5. PowerPC Processor Core

5-25

Cache Implementation

5.4.3.2 Processor Responses to PCI-to-Memory Transactions

The CCU controls the data flow between the PCI interface and the memory interface. One

of its functions is to broadcast these transactions on the peripheral logic bus so that the

processor core can snoop the L1 cache as needed (if snooping is enabled). Table 5-5 shows

all the types of transactions reflected by the CCU to the processor core for snooping.

stwcx., reservation set

CCU takes no further action.

(The MPC8240 does not support atomic

references in PCI memory space.)

tlbsync

CCU takes no further action.

Graphic write (ecowx)

Processor transaction error. Machine check

signalled to processor core (if enabled)

Graphic read (eciwx)

Processor transaction error. Machine check

signalled to processor core (if enabled)

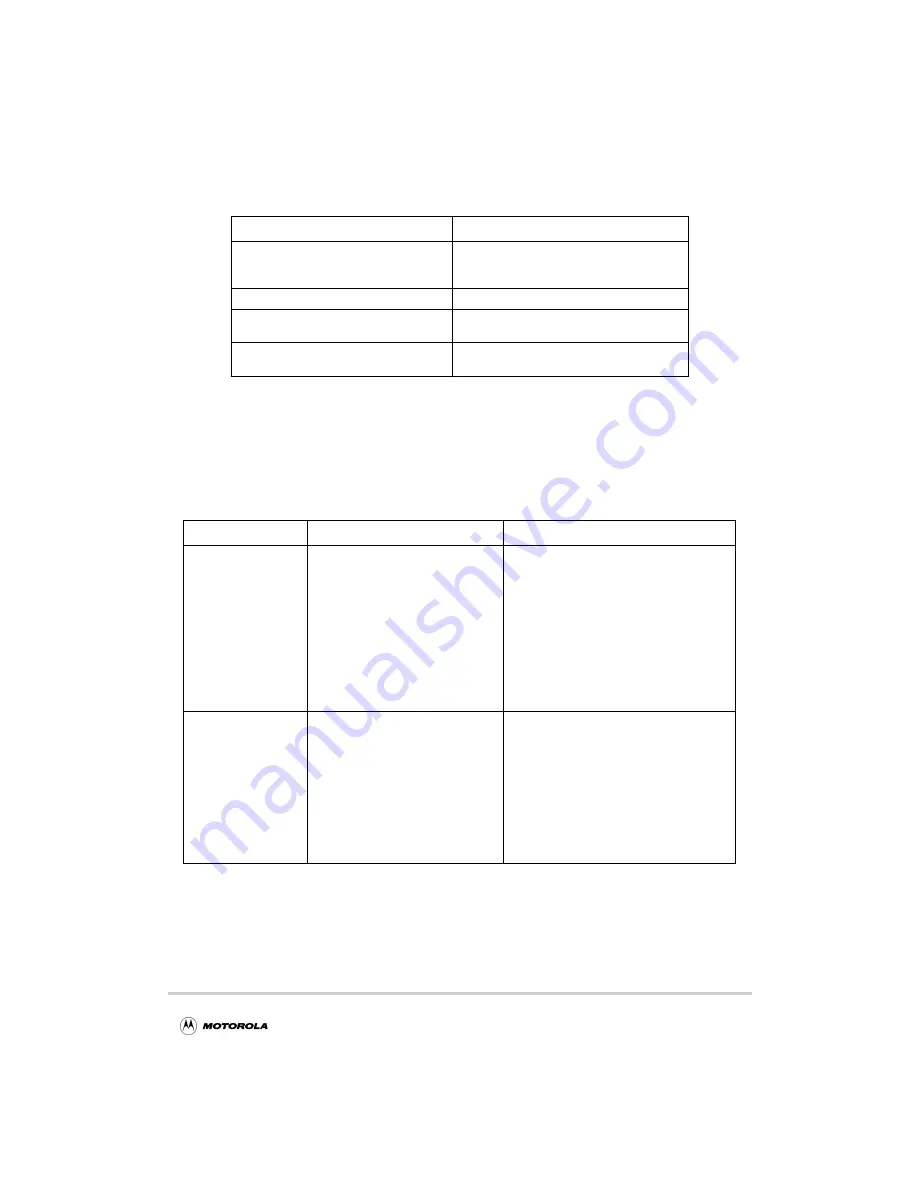

Table 5-6. Transactions Reflected to the Processor for Snooping

Snooped Transaction

Condition Detected by CCU

Processor Response

Read

Non-locked PCI read from memory

All burst reads observed on the bus are

snooped as if they were writes, causing the

addressed cache block to be flushed. A read

marked as global causes the following

responses:

• If the addressed block in the cache is invalid,

the processor takes no action.

• If the addressed block in the cache is in the

exclusive state, the block is invalidated.

• If the addressed block in the cache is in the

modified state, the block is flushed to memory

and the block is invalidated.

Read-with-intent-to-mo

dify (RWITM)-atomic

Locked PCI read from memory

A RWITM operation is issued to acquire

exclusive use of a memory location for the

purpose of modifying it.

• If the addressed block is invalid, the

processor takes no action.

• If the addressed block in the cache is in the

exclusive state, the processor changes the

state of the cache block to invalid.

• If the addressed block in the cache is in the

modified state, the block is flushed to memory

and the block is invalidated.

Table 5-5. CCU Responses to Processor Transactions (Continued)

Processor Transaction

CCU Response

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...