5-34

MPC8240 Integrated Processor User’s Manual

Differences between the MPC8240 Core and the PowerPC 603e Microprocessor

5.8 Differences between the MPC8240 Core and the

PowerPC 603e Microprocessor

The MPC8240 processor core is a derivative of the MPC603e microprocessor design. Some

changes have been made and are visible either to a programmer or a system designer. Any

software designed for an MPC603e is functional when replaced with the MPC8240 except

for the specific customer-visible changes listed in Table 5-10.

Software can distinguish between the MPC603e and the MPC8240 by reading the

processor version register (PVR). The MPC8240’s processor version number is 0x0081; the

processor revision level starts at 0x0100 and is incremented for each revision of the chip. It

is expected that this information is most useful for programmers writing data cache flush

routines.

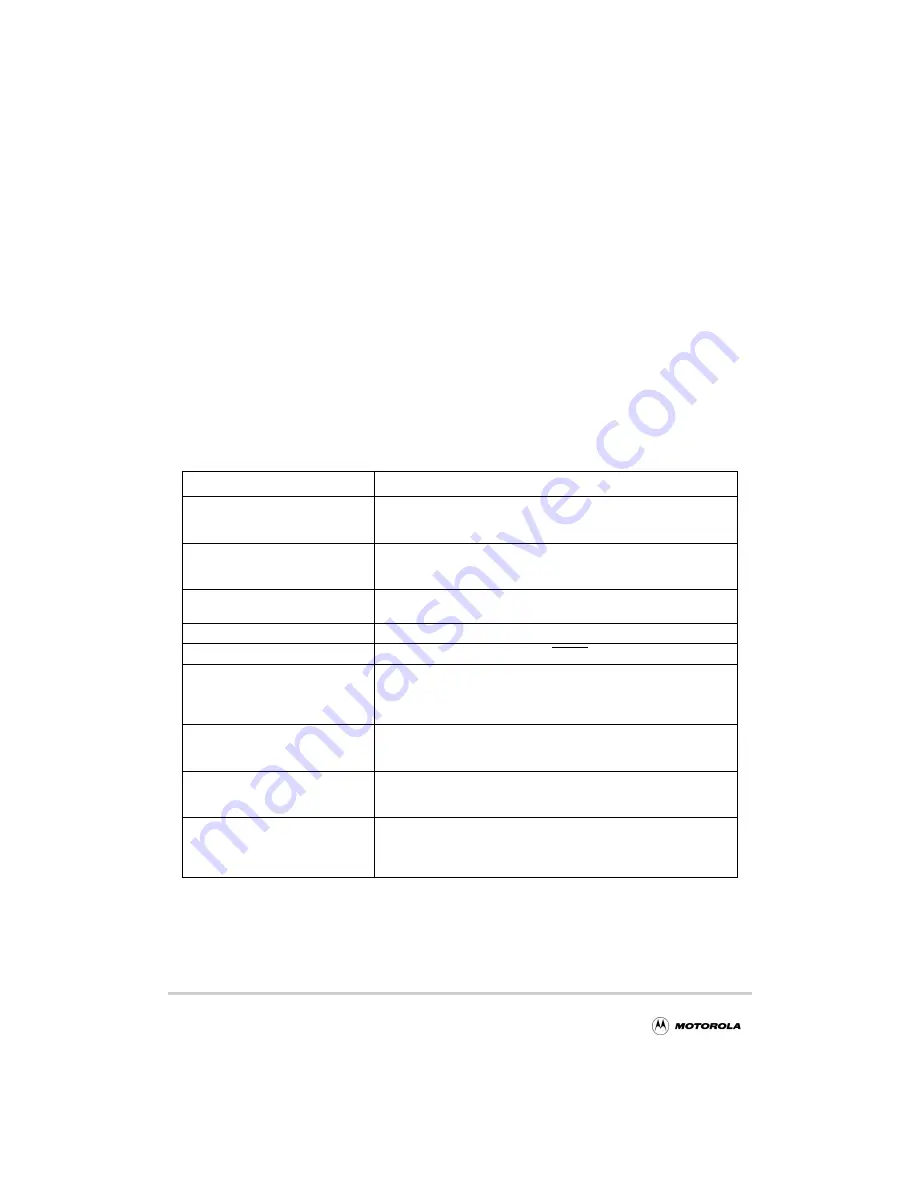

Table 5-10. Major Differences between MPC8240’s Core and the MPC603e User’s

Manual

Description

Impact

Changed HID1 to add bus frequency

multipliers as described in the

MPC8240 Hardware Specification

On extra bit is provided for PLL configuration, and some other unused

encodings of the PLL_CFG[0–4] are now defined.

Added hardware support for

misaligned little endian accesses

Except for strings/multiples, little-endian load/store accesses not on a

word boundary generate exceptions under the same circumstances as

big-endian accesses.

Removed misalignment support for

eciwx and ecowx instructions.

These instructions cause an alignment exception if the operands are not

on a word boundary.

Removed HID0[5]; now reserved

There is no support for ICE pipeline tracking.

Removed HID0[7]; now reserved

No impact, as the MPC8240 has no ARTRY signal.

Added instruction and data cache

locking mechanism

Implements a cache way locking mechanism for both the instruction and

data caches. One to three of the four ways in the cache can be locked with

control bits in the HID2 register. See Section 5.3.1.2.3, “Hardware

Implementation-Dependent Register 2 (HID2).”

Improved access to cache during

block fills

The MPC8240 provides quicker access to incoming data and instruction

on a cache block fill. See Section 5.4.2, “MPC8240

Implementation-Specific Cache Implementation.”

Improved integer divide latency

Performance of integer divide operations has been improved in the

processor core. A divide takes half the cycles to execute as described in

MPC603e User’s Manual. The new latency is reflected in Table 5-9.

No support for dcbz instruction in

areas of memory that are

write-through and can be accessed by

multiple logical addresses

This was previously documented as an anomaly in the MPC603e. Stores

of zeros must be used instead of the dcbz instruction when the memory

area is designated as write-through, coherency required.

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...