Chapter 6. MPC8240 Memory Interface

6-31

SDRAM Interface Operation

6.2.12 SDRAM Refresh

The memory interface supplies CBR refreshes to SDRAM according to the interval

specified in MCCR2[REFINT]. REFINT is the refresh interval. When REFINT expires and

the memory bus is idle, the MPC8240 issues a precharge and then a refresh command to

the SDRAM devices. However, if the memory bus is busy with a transaction, the refresh

request is not performed and an internal, 4-bit, missed-refresh counter is incremented. The

refresh interval timer is reset to the value in REFINT and the process begins again. When

the refresh interval counter expires and the bus is idle, the MPC8240 performs all the

missed refreshes back-to-back and the missed refresh counter is cleared. If the number of

missed refreshes exceeds 16, the counter overflows and causes a refresh overflow error. See

Section 13.3.2.4, “Memory Refresh Overflow Error,” for more information about the

reporting of these errors. In the worst case, the MPC8240 misses 16 refreshes and must

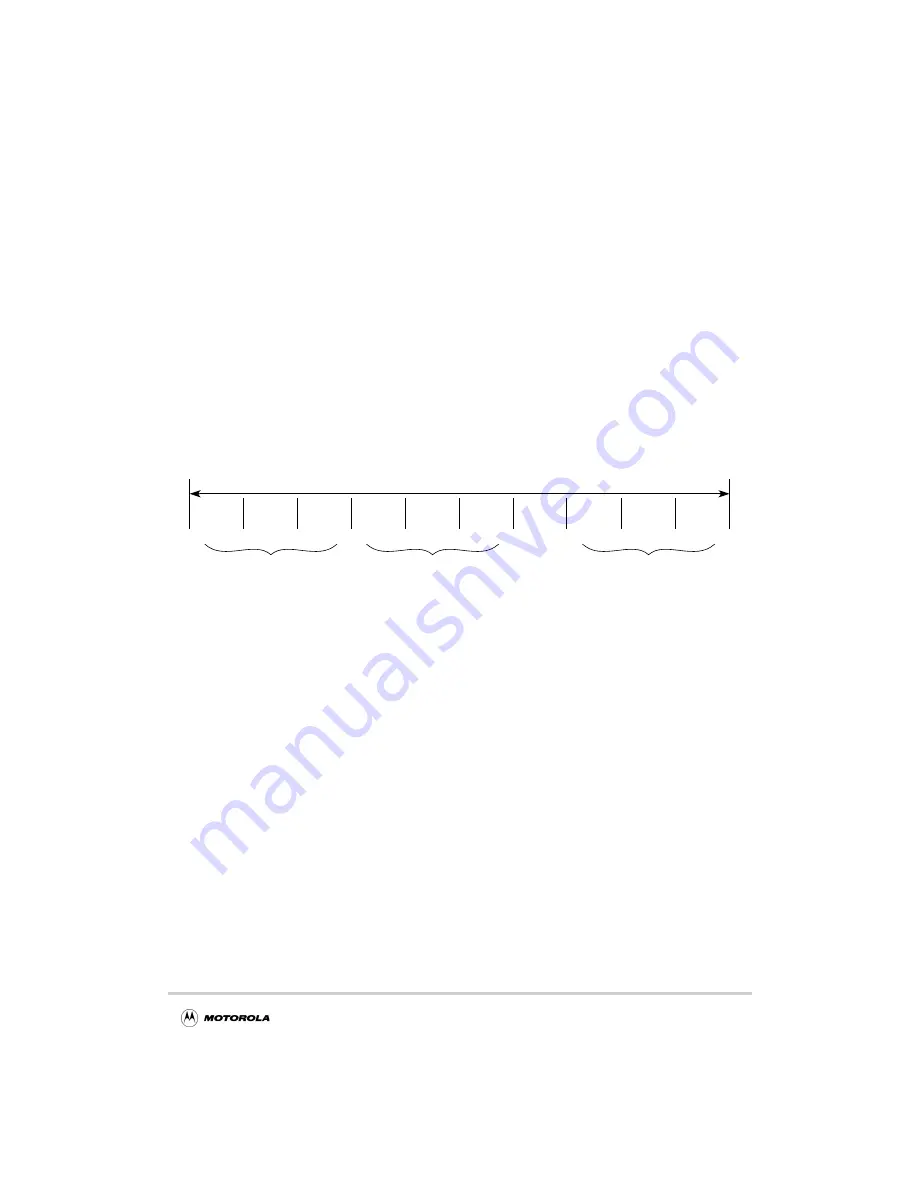

perform all 16 refreshes. Figure 6-17 shows this worst case situation repeated over the

device’s refresh period.

Figure 6-17. SDRAM Refresh Period

The value stored in REFINT must permit the MPC8240 to supply refreshes within the

refresh period specified by the SDRAM device. Another factor in calculating the value for

REFINT is the overhead for the MPC8240 to actually issue a refresh command to the

SDRAM device. The MPC8240 has to precharge any open banks before it can issue the

refresh command. The MPC8240 requires two clock cycles to issue a precharge to an

internal bank; with the possibility of four banks open simultaneously, this equates to eight

clock cycles. The MPC8240 must also wait for the PRETOACT interval to pass before

issuing the refresh command. The refresh command itself takes four clock cycles (see

Figure 6-18) with a dead cycle needed between subsequent refresh commands.

REFINT must also allow for a potential collision between memory accesses and refresh

cycles. In the worst case, the refresh may have to wait the number of clock cycles required

by the longest access. For example, if a local ROM access is in progress at the time a refresh

operation needs to be performed, the refresh must wait until the ROM access has

completed. If ROM is local, the longest access that could potentially stall a refresh is a burst

read from ROM. If ROM is located on the PCI bus, the longest memory access is a burst

read from the SDRAM.

16

REFINT

misses

Time to

perform

16

refreshes

Worst

case

memory

access

1

16

REFINT

misses

Time to

perform

16

refreshes

Worst

case

memory

access

2

. . .

16

REFINT

misses

Time to

perform

16

refreshes

Worst

case

memory

access

n+1

Refresh Period (RP)

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...