Chapter 6. MPC8240 Memory Interface

6-55

FPM or EDO DRAM Interface Operation

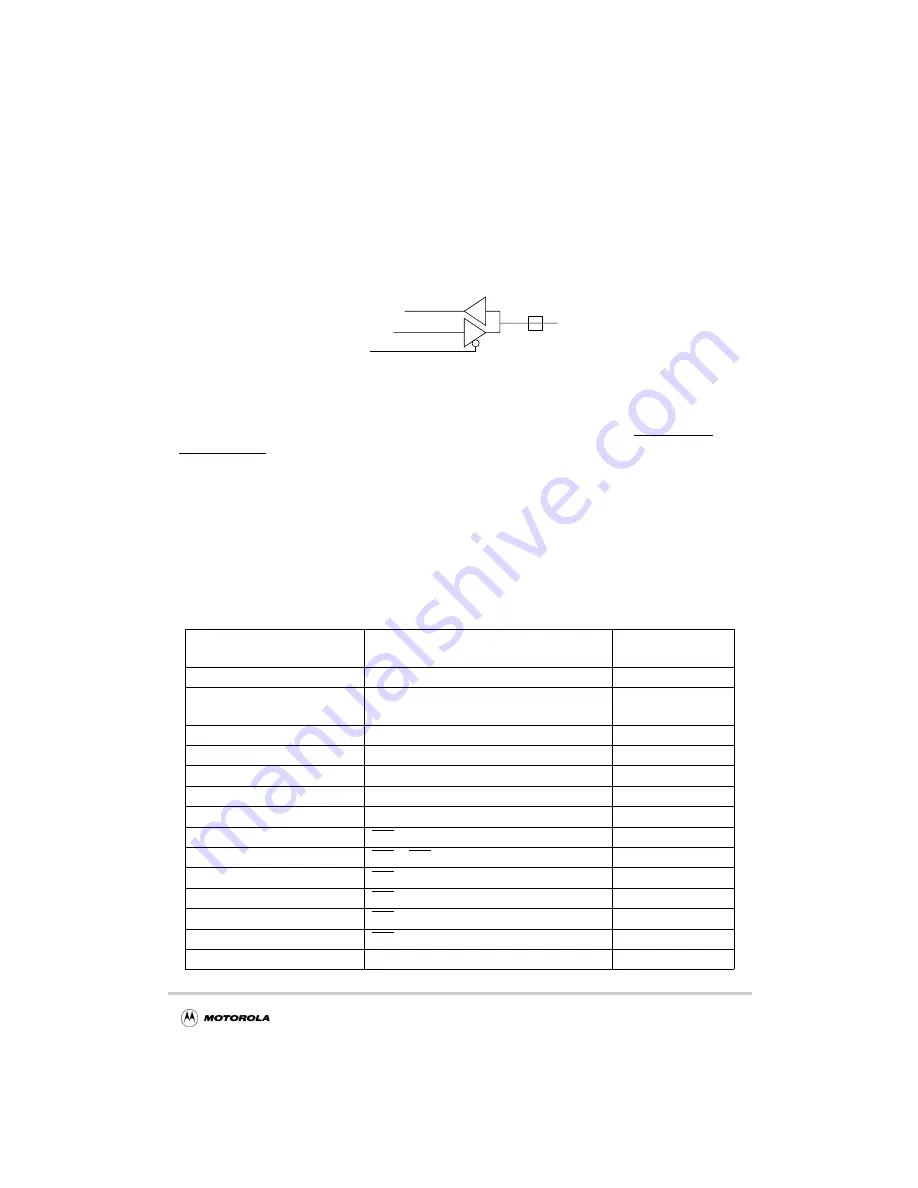

The data path between the internal processor bus to the external memory bus in

flow-through mode is shown in Figure 6-34. The flow-through mode is the default data bus

buffering mode for the MPC8240.

Note that in-line ECC is not available with FPM or EDO DRAM.

Figure 6-34. FPM-EDO Flow-through Memory Interface

6.3.4 FPM or EDO DRAM Initialization

At system reset, the main memory is inactive. When the reset signals (HRST_CPU and

HRST_CTRL) are negated, the MEMGO bit is cleared to zero (0) which turns off the

memory controller. The processor 5core starts fetching boot code from ROM (local or PCI).

For systems containing FPM or EDO DRAM, the boot code must set the MPC8240

configuration bit RAMTYP = 1.

Additionally, all other MPC8240 configuration registers relevant to DRAM must be

initialized. Table 6-21 shows the register fields in the memory interface configuration

registers (MICRs) and the memory control configuration registers (MCCRs).

Table 6-21. Memory Interface Configuration Register Fields

Register Field

Description

Configuration

Register (and offset)

RAM_TYPE

SDRAM, FPM, or EDO DRAM

MCCR1 @ <F0>

Memory Bank

Start and End Addresses

MICR @ <80>–<9C>

Memory Bank Enables

MICR @ <A0>

Row Address Bits For Each Bank

MCCR1 @ <F0>

PCKEN

Parity check enable

MCCR1 @ <F0>

SREN

Self refresh enable

MCCR1 @ <F0>

REFINT

Interval between refreshes

MCCR2 @ <F4>

RP1

RAS precharge interval

MCCR3 @ <F8>

RCD2

RAS to CAS delay

MCCR3 @ <F8>

CAS3

CAS assertion interval for first data beat

MCCR3 @ <F8>

CP4

CAS precharge interval

MCCR3 @ <F8>

CAS5

CAS assertion interval for page mode data beats

MCCR3 @ <F8>

RAS6P

RAS assertion interval for CBR refresh

MCCR3 @ <F8>

RMW_PAR

Read modify write parity

MCCR2 @ <F4>

DRAM data path

Processor data from DRAM

signals

Processor data to DRAM

Output enable

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...