6-22

MPC8240 Integrated Processor User’s Manual

SDRAM Interface Operation

The value of the above six parameters, (in whole clock cycles) must be set by boot code at

system start-up and kept in the MPC8240 configuration register space.

The following figures show SDRAM timing for various types of accesses. Figure 6-8 shows

a single-beat read operation.

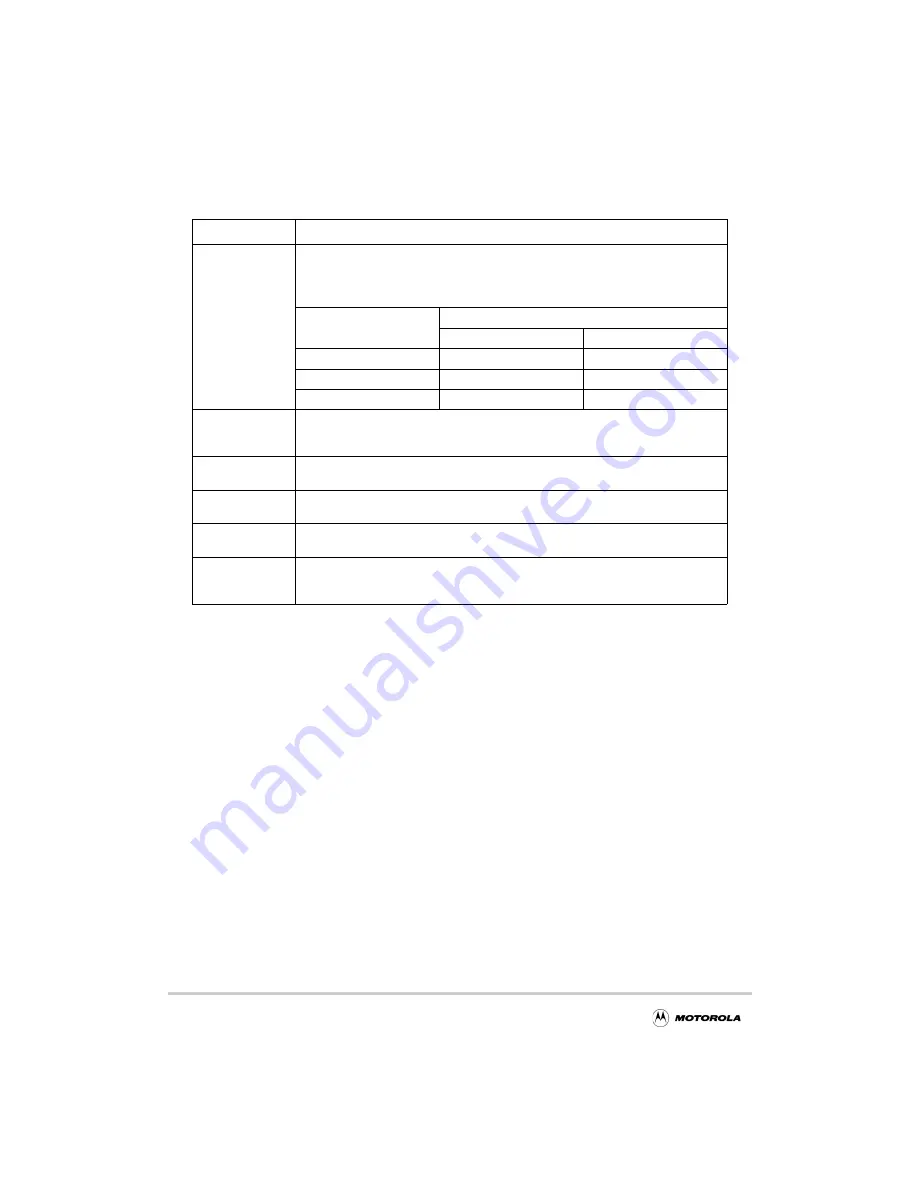

Table 6-11. SDRAM Interface Timing Intervals

Timing Intervals

Definition

RDLAT

The number of clock cycles from the read column command until the first data beat is

available on the internal processor core data bus.

RDLAT = SDRAM CAS l buffer mode delay + delay due to REGDIMM value. The

value of RDLAT should be additionally increased by one if MCCR3[REGDIMM] = 1.

RDLAT Mode

MCCR3[REGDIMM]

0

1

Flow through

CL

–

Registered

CL + 1

CL + 2

In-line ECC

CL + 2

CL + 3

REFREC

The number of clock cycles from the refresh command until an activate command is

allowed. This can be calculated by referring to the AC specification of the SDRAM device.

The AC specification indicates a minimum refresh to activate interval in nanoseconds.

ACTORW

The number of clock cycles from an activate command until a read or write command is

allowed. This interval will be listed (nS) in the AC specifications of the user’s SDRAM.

ACTOPRE

The number of clock cycles from an activate command until a precharge command is

allowed. This interval will be listed (nS) in the AC specifications of the user’s SDRAM.

PRETOACT

The number of clock cycles from a precharge command until an activate command is

allowed. This interval will be listed (nS) in the AC specifications of the user’s SDRAM.

BSTOPRE

The number of clock cycles to maintain a page open after an access. A subsequent

access can generate a page hit during this interval. A page hit reloads the BSTOPRE

counter. When the interval expires, a precharge is issued to the page.

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...