Chapter 11. Embedded Programmable Interrupt Controller (EPIC) Unit

11-17

Register Definitions

Table 11-6 describes the bit settings for the GCR.

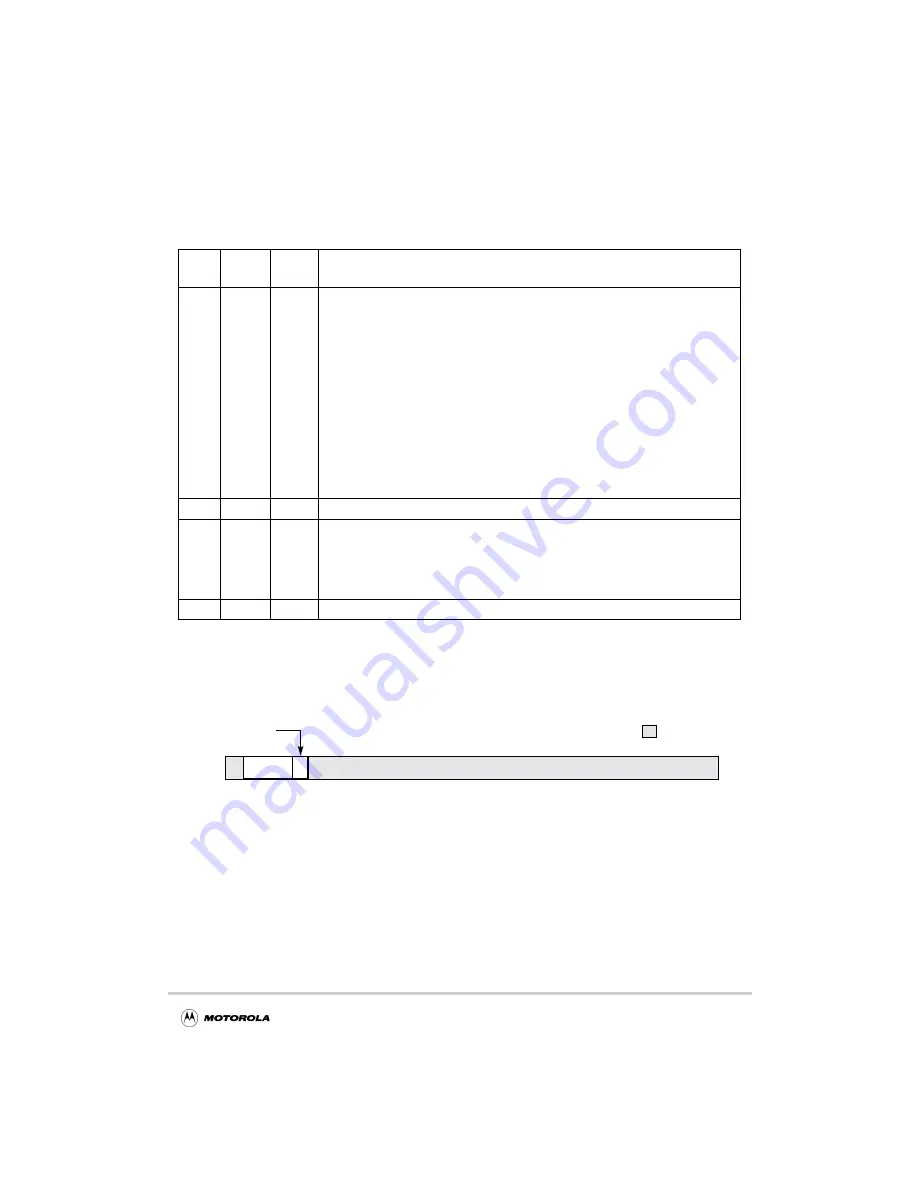

11.9.3 EPIC Interrupt Configuration Register (EICR)

The EICR provides programming control for the serial interrupt mode and the serial clock

frequency. Note that this register is read/write. Figure 11-6 shows the bits in the EICR.

Figure 11-6. EPIC Interrupt Configuration Register (EICR)

Table 11-6. GCR Field Descriptions—Offset 0x4_1020

Bits

Name

Reset

Value

Description

31

R

0

Reset EPIC unit. Writing a one to this bit resets the EPIC controller logic. This bit is

cleared automatically when this reset sequence is complete. Setting this bit causes the

following:

• All pending and in-service interrupts are cleared.

• All interrupt mask bits are set.

• All timer base count values are reset to zero and count inhibited.

• The processor current task priority is reset to 0xF thus disabling interrupt delivery to

the processor.

• Spurious vector resets to 0xFF.

• EPIC defaults to pass-through mode.

• The serial clock ratio resets to 0x4.

All other registers remain at their pre-reset programmed values.

30

—

0

Reserved

29

M

0

Mode

0 Pass-through mode. EPIC is disabled and interrupts detected on IRQ0 (active-high)

are passed directly to the processor core.

1 Mixed-mode. When this bit is set, EICR[SIE] determines whether the EPIC unit is

operating in direct or serial interrupts mode.

28–0

—

All 0s

Reserved

0

R

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

31 30

28 27 26

0

Reserved

SIE

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...