Chapter 15. Debug Features

15-7

Memory Debug Address

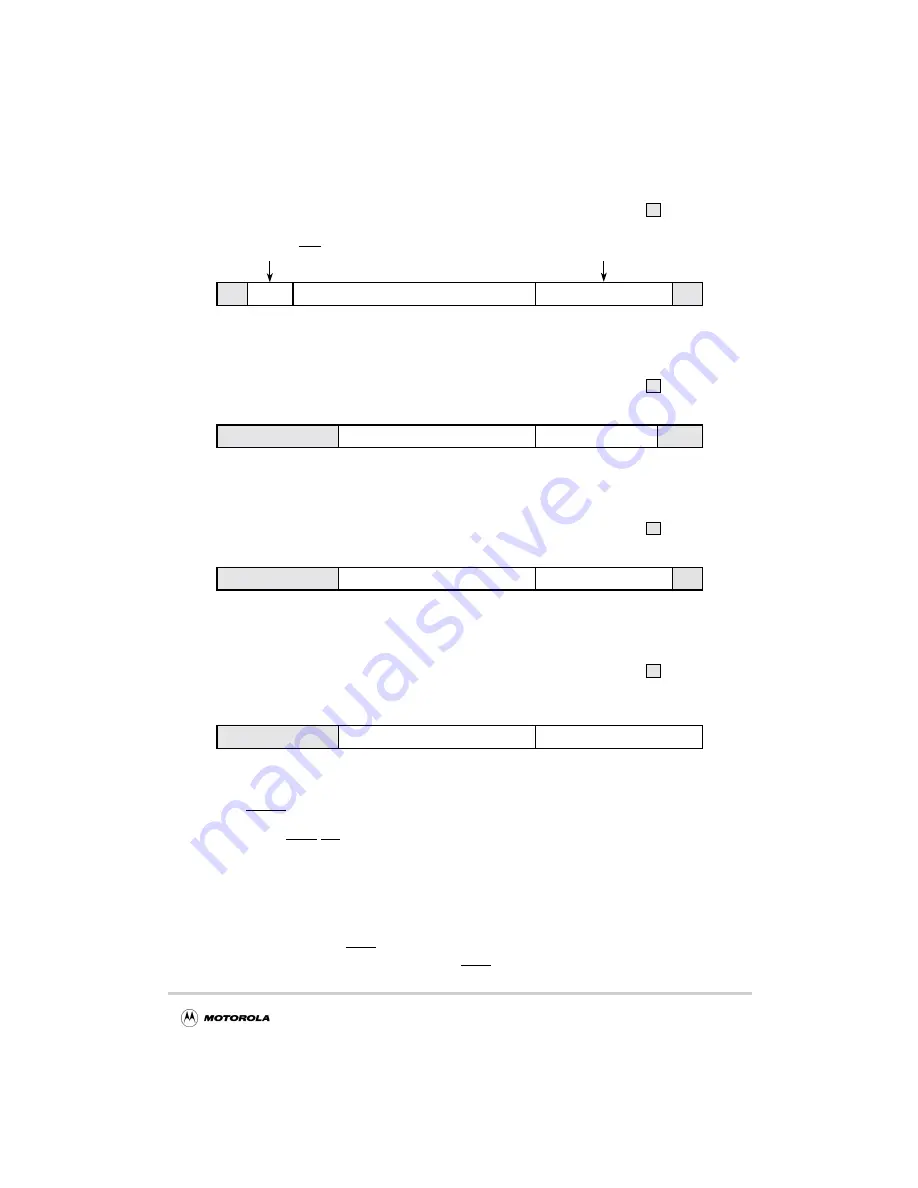

Figure 15-4. 32-Bit Mode, DRAM and SDRAM Physical Address for Debug

Figure 15-5. 64-Bit Mode, ROM and Flash Physical Address for Debug

Figure 15-6. 32-Bit Mode, ROM and Flash Physical Address for Debug

Figure 15-7. 8-Bit Mode, ROM and Flash Physical Address for Debug

15.3.4 RAS Encoding

The encoding of RAS/CS[0:7] to form bits 29–27 of the physical address for DRAM and

SDRAM transactions is based on the memory bank configuration as programmed in the

bank starting and ending address configuration registers located at offsets 0x80, 0x84,

0x88, 0x8C, 0x90, 0x94, 0x98, and 0x9C. For this encoding algorithm to be deterministic,

DRAM and SDRAM banks are not allowed to cross a 128-Mbyte address partition (that is,

the starting and ending address for any one bank must fall within the same 128-Mbyte

partition). Obviously, such RAS information is relevant only for DRAM (and SDRAM) and

not for ROM/Flash. For a simple example of RAS encodings, see Table 15-6 below.

0 0

DA[15:0]

0 0

31 30 29

27 26

11 10

3

2

1

0

Reserved

Encoded version of RAS[0:7]

SDMA[8:0] of column address

1 1 1 1 1 1 1 1

DA[12:0]

AR[7:0] of address

0 0 0

31 30 29 30 27 26 25 24 23

11 10

3

2

1

0

Reserved

1 1 1 1 1 1 1 1

DA[12:0]

AR[8:0] of address

0 0

31 30 29 30 27 26 25 24 23

11 10

2

1

0

Reserved

1 1 1 1 1 1 1 1

DA[12:0]

AR[10:0] of address

31 30 29 30 27 26 25 24 23

11 10

0

Reserved

Summary of Contents for MPC8240

Page 1: ...MPC8240UM D Rev 1 1 2001 MPC8240 Integrated Processor User s Manual ...

Page 38: ...xviii MPC8240 Integrated Processor User s Manual TABLES Table Number Title Page Number ...

Page 48: ...xlviii MPC8240 Integrated Processor User s Manual Acronyms and Abbreviations ...

Page 312: ...6 94 MPC8240 Integrated Processor User s Manual ROM Flash Interface Operation ...

Page 348: ...7 36 MPC8240 Integrated Processor User s Manual PCI Host and Agent Modes ...

Page 372: ...8 24 MPC8240 Integrated Processor User s Manual DMA Register Descriptions ...

Page 394: ...9 22 MPC8240 Integrated Processor User s Manual I2O Interface ...

Page 412: ...10 18 MPC8240 Integrated Processor User s Manual Programming Guidelines ...

Page 454: ...12 14 MPC8240 Integrated Processor User s Manual Internal Arbitration ...

Page 466: ...13 12 MPC8240 Integrated Processor User s Manual Exception Latencies ...

Page 516: ...16 14 Watchpoint Trigger Applications ...

Page 538: ...B 16 MPC8240 Integrated Processor User s Manual Setting the Endian Mode of Operation ...

Page 546: ...C 8 MPC8240 Integrated Processor User s Manual ...

Page 640: ...INDEX Index 16 MPC8240 Integrated Processor User s Manual ...