Copyright © Siemens AG 2016. All rights reserved

124

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

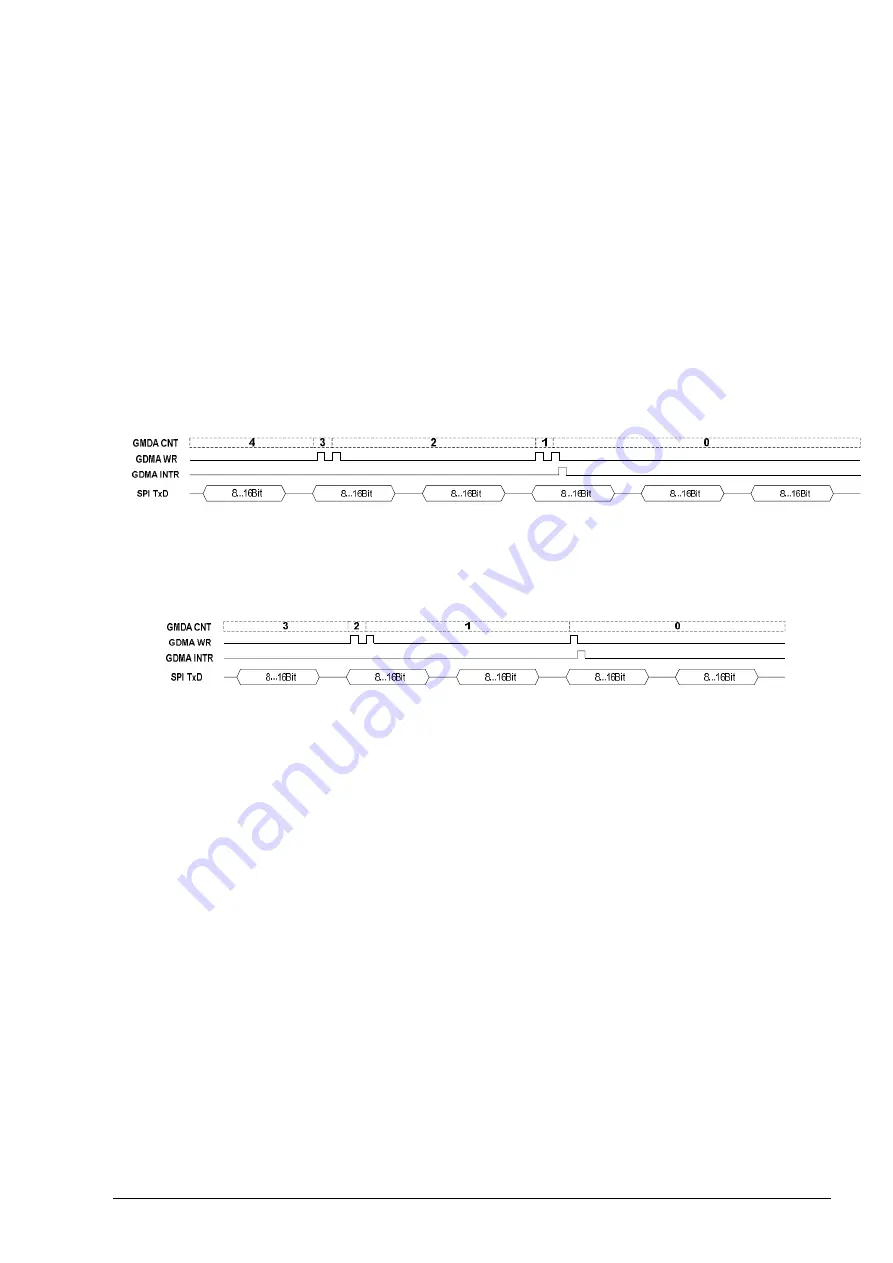

As a result of the posted response at the AHB interface of the GDMA, the GDMA interrupt

generation behavior for SPI data transfer varies depending on the transfer mode at the

AHB (single / burst mode).

In

single transfers

, the first instance of write access to the SPI-IP is acknowl-

edged at the GMDA immediately by the ML-AHB (posted behavior) even before it

is entered in the SPI transmit FIFO. As TFE (Transmit FIFO Empty) is not yet re-

set, another instance of write access to the SPI-IP is triggered and implemented by

the GDMA despite single transfer.

Consequence:

Despite single mode, up to 2 user data transfers to the SPI-IP can

be carried out by the GDMA (behavior in this case corresponds to an INCR2

burst). This means that:

o

when the number of data transfers is even, the GDMA interrupt always be-

comes active 3 SPI transfers (8…16 bits) before the end of the SPI transfer

1 SPI transfer in the SPI shift re 2 SPI transfers in the SPI trans-

mit FIFO

o

when the number of data transfers is odd, the GDMA interrupt always be-

comes active 2 SPI transfers (8…16 bits) before the end of the SPI transfer

1 SPI transfer in the SPI shift re 1 SPI transfer in the SPI transmit

FIFO

In

burst transfers

, complete burst access (INCR, INCR4, INCR8, …) is always to

the SPI-IP. The user must therefore ensure that the number of items of user data

entered in the SPI transmit FIFO by the GDMA does not result in a FIFO overflow.

As the first user data transfer in burst access resets TFE (Transmit FIFO Empty),

this information is available at the GDMA at the end of burst access and ensures

that there is no further GDMA write access

Consequence:

In burst mode, the GDMA can carry out user data transfers to the

SPI-IP of up to the AHB burst length. This makes the GDMA interrupt active up to

"AHB burst 1" before the end of the SPI transfer.

The GDMA interrupt can be generated independently of the user data to be transferred if

the final user data transfer to be carried out with the SPI is processed with its own trans-

fer element in the GDMA job. As in this case the GDMA must first read the next transfer

element over the AHB, TFE (Transmit Fifo Empty) is reset by the SPI-IP until the time of

the actual single transfer so that the GDMA does not transmit this last instance of write

access to the SPI-IP until TFE (Transmit Fifo Empty) is set again, which is always the

case when there are no more data in the SPI transmit FIFO. The GDMA interrupt there-

fore always becomes active 2 SPI transfers (8…16 bits) before the end of the SPI trans-

fer.