Copyright © Siemens AG 2016. All rights reserved

191

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

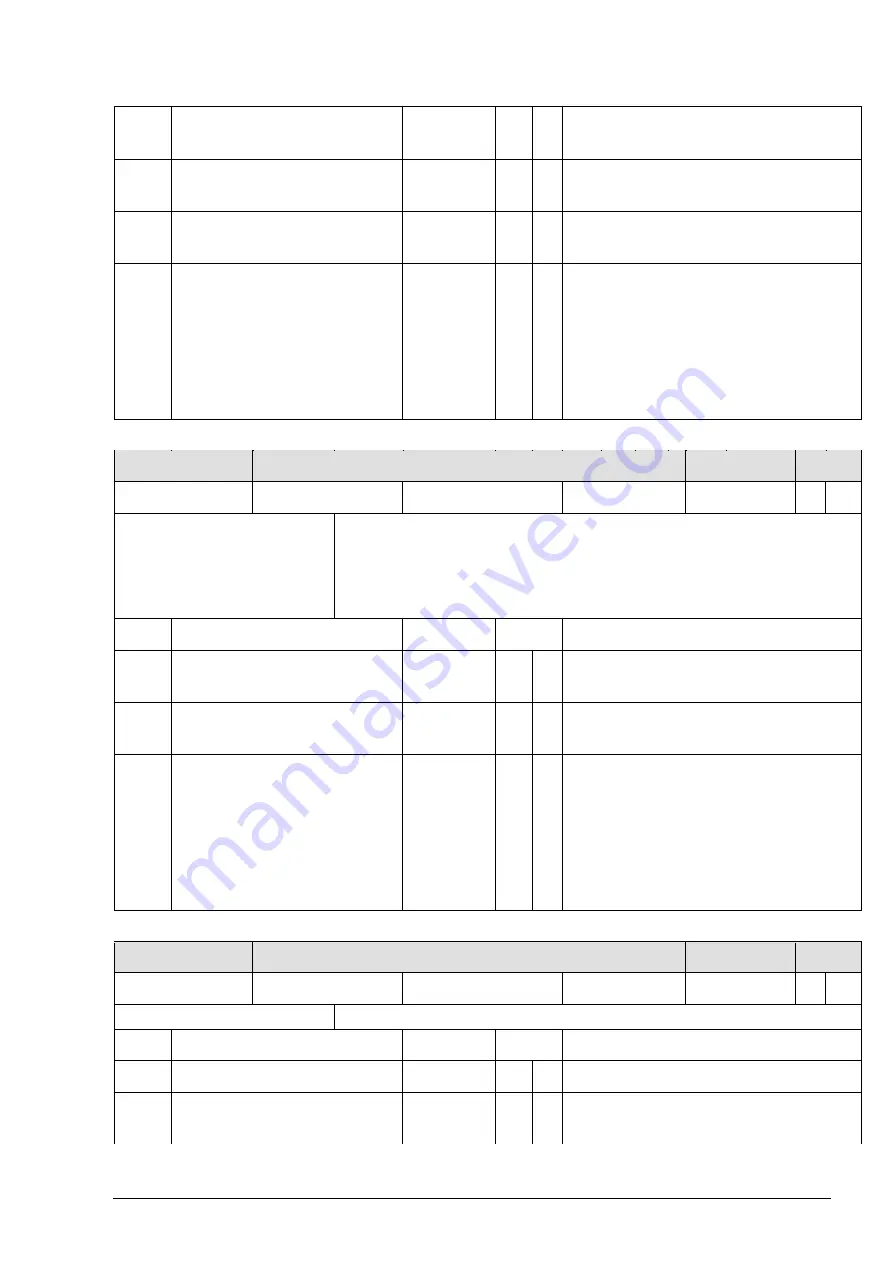

27dt8 <reserved>

00000h r The higher-value APB address

bits(31:8) are mirrored in the HostIF

29dt28 APB_SIZE

2h

r

"10": Word access (32-bit) ?? fixed

value as only word access possible

30

APB_RD_WR

0h

r

'0': RD access

'1': WR access

31

ERROR_LOCK

0h

r w

Set to '1' by the HW if erroneous

APB access is

detected. Further HW entries are

then blocked.

The SW must reset the bit to '0' to

enable

new entries.

Register:

XHIF_CONTROL

Address:

70h

Bits:

3dt0

Reset value:

0h

Attributes: rh w

Description:

XHIF Interface Settings

After reset

and when the SCRB CONFIG_REG register is written, these

settings

are taken from the register

Bit

Identifier

Reset

Attr.

Function / Description

0

XHIF_ACC_MODE

0h

rh w XHIF Handshake protocol: 0 =Intel

Mode, 1 =Motorola Mode

1

XHIF_POL_RDY

0h

rh w '0': XHIF_XRDY is low_aktiv

'1': XHIF_XRDY is high_aktiv

3dt2 XHIF_CPU_WIDTH

0h

rh w

Data bus width:

00 =8b *,

01 =16b,

10 =32b,

11 =32b

* 00 =8b is however not supported

by the XHIF interface.

Register:

XHIF_0_P0_RG

Address:

80h

Bits:

31dt0

Reset value:

0h

Attributes: r (w)

Description:

Range value of the page #0

Bit

Identifier

Reset

Attr.

Function / Description

7dt0 XHIF_0_P0_RG_ROSL2 00h

r

Read only value = 0

21dt8 XHIF_0_P0_RG_RW

0000h

r w Read/Write part of the Range regis-

ter