Copyright © Siemens AG 2016. All rights reserved

155

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

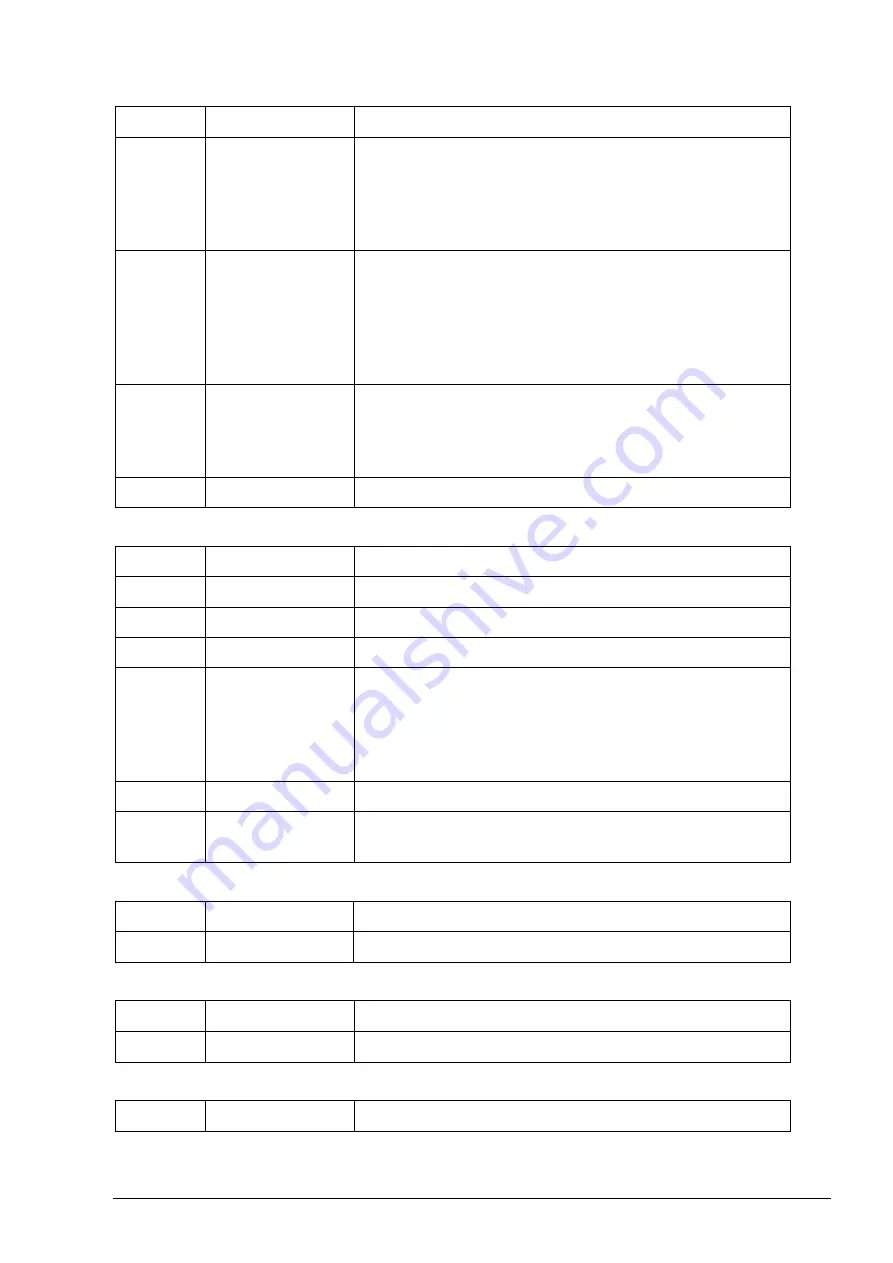

31:24

reserved

23:22

SRC_AMODE

Source Address Mode

00 = increment address

10 = hold address

x1 = reserved for future implementation = hold ad-

dress

21:20

DEST_AMODE

Destination Address Mode (reserved = hold ad-

dress)

00 = increment address

10 = hold address

x1 = reserved for future implementation = hold ad-

dress

19:18

BURST_MODE

00 = Single

01 = INCR4

10 = INCR8

11 = INCR16

17:16

reserved

DMA Transfer Record – Transfer Count

Bit no.

Name

Description

31

LAST_TR

Last Transfer of the Job

30

EN_DMA_ACK

1 = set output HW_DMA_ACK if transfer is finished

29:24

reserved

23:22

ESIZE

Element size

00 = 8bit

01 = 16 bit

10 = 32 bit

11 = reserved

21:16

reserved

15:0

TR_COUNT

Transfer Count

0x0 = 1 element, 0xFFFF = 65536 elements

DMA Stack – Source Address Stack

Bit no.

Name

Description

31:0

CSRC

Current Source Address

DMA Stack – Destination Address Stack

Bit no.

Name

Description

31:0

CDEST

Current Destination Address

DMA Stack – Transfer Control Stack

Bit no.

Name

Description