Copyright © Siemens AG 2016. All rights reserved

53

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

Byte and halfword write access to addresses that can be written word by

word

As an example, here is the SCRB access error register:

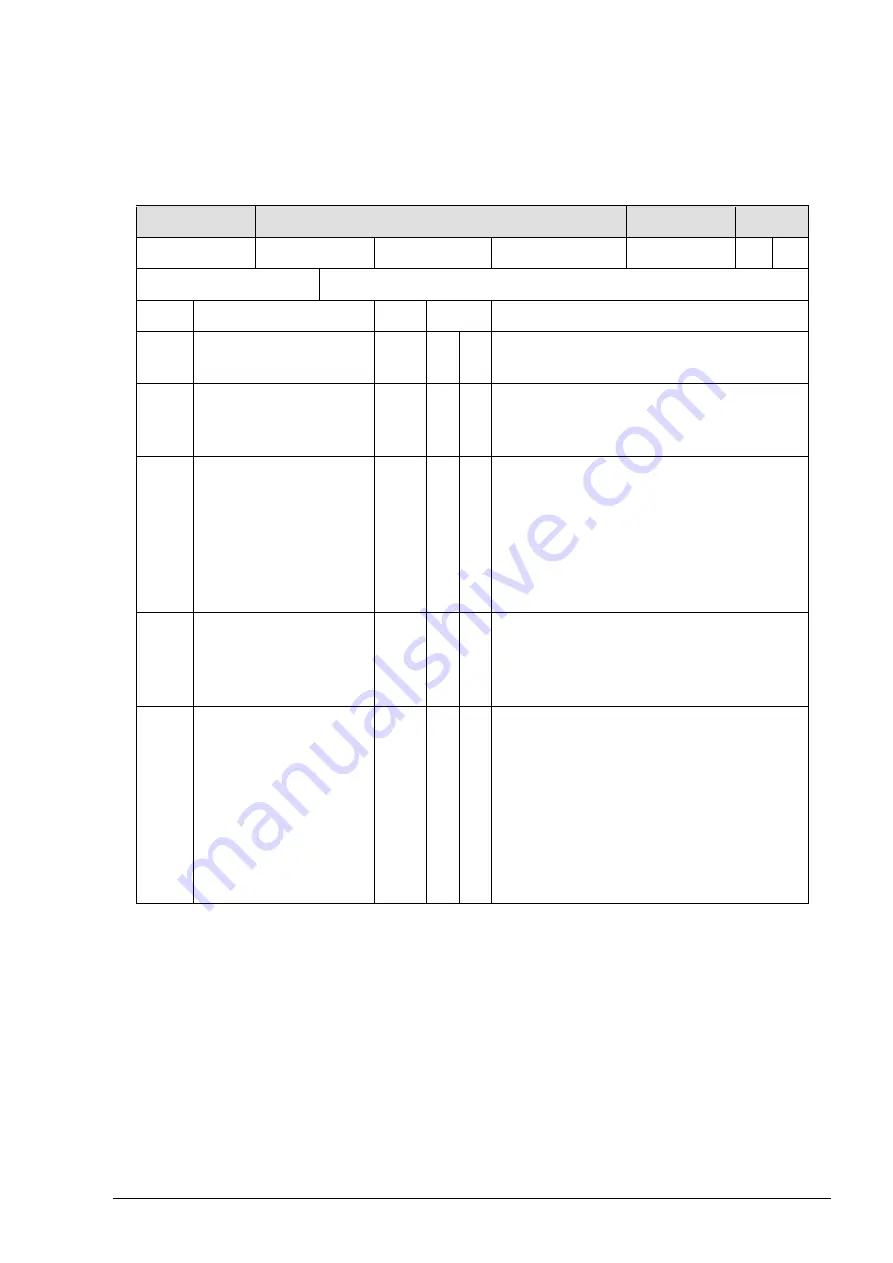

Register:

SCRB_ACC_ERR

Address:

38h

Bits:

31dt0

Reset value: 8000000h

Attributes: r(h) (w)

Description:

Access Error Register

Bit

Identifier

Reset Attr.

Function / Description

15dt0 ACCESS_ADDR

0000h rh

Address that caused the last access

error.

27

ACCESS_BUS_TYPE 1h r

Businterface that caused the last ad-

dress error.

1 = APB-Interface.

29dt28 ACCESS_SIZE

0h

rh

Shows the transfers size during the last

access error.

00 = 8 bit transfer

01 = 16 bit transfer

10 = 32 bit transfer

11 = illegal combination of APB byte

enables

30

ACCESS_TYPE

0h

rh

Shows the transfer type during the last

access error.

0 = read transfer

1 = write transfer

31

ERR_LOCK

0h rh w

The hardware sets this bit during an

access error. The bit remains set as

long as the software does not write a

logic 0 into this bit. As long as the bit is

set, the content of the register remains

unchanged even during further access

errors.

Read:

1 = Access Error

Table 8: Access Error Register (from SCRB)

Implementation in ERTEC 200P top level:

The

access_err_irq_o

events of the individual modules are high-active for

a 125 MHz system

clock

in the top level and are all set out in the MODUL_ACCESS_ERR register (see

2.3.10.9.5).

An entry in MODUL_ACCESS_ERR triggers the ARM926 interrupt 'Modul_Access_Error'

(see 2.3.2.14). Following a MODUL_ACCESS_ERROR interrupt, the SW must read the

MODUL_ACCESS_ERR register to identify the module affected. The SW must then read

the detailed data for the erroneous access from the access error register in the relevant