Copyright © Siemens AG 2016. All rights reserved

129

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

2.3.4.5 Register Description

A description of the registers can be found in the specifications: /55/.

Note: The "notused" register bits can also be written, unlike in the IP specifications.

The data-bus-width of all specified registers in this module is: 32.

A '0' is read from Software for each not specified Bit in the registers.

The addressing is organized: WORD - wise

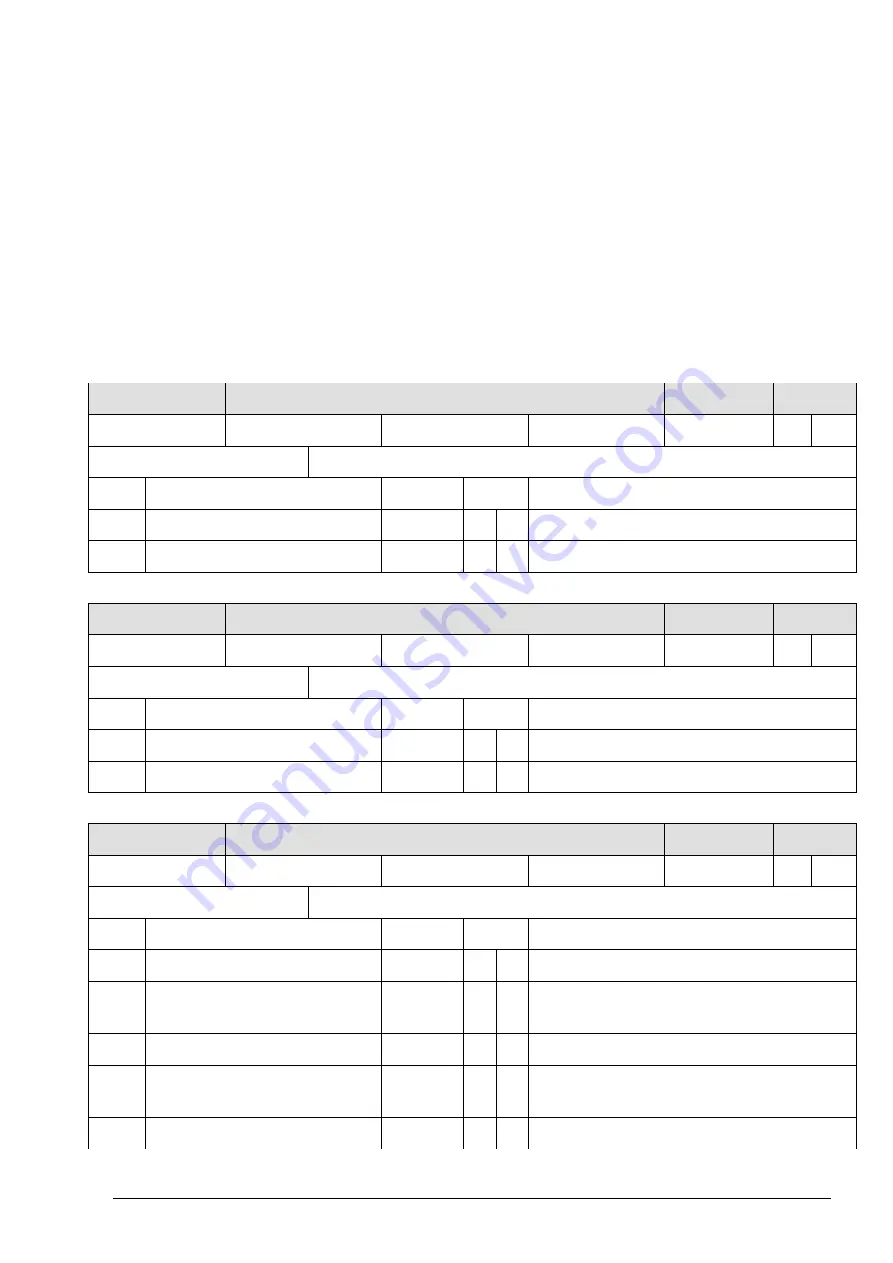

Module: /gdma

Register:

GDMA_REG_ADDR

Address:

0h

Bits:

31dt0

Reset value:

00000000h

Attributes: r (w)

Description:

GDMA Register Base Address

Bit

Identifier

Reset

Attr. Function

/

Description

3dt0 <notused>

0h

r

all bits

= '0'

31dt4 REG_ADDR

0000000h r w DMA Register Base Address

Register:

GDMA_LIST_ADDR

Address:

4h

Bits:

31dt0

Reset value:

00000000h

Attributes: r (w)

Description:

DMA Transfer List Base Address

Bit

Identifier

Reset

Attr. Function

/

Description

3dt0 <notused>

0h

r

all bits

= '0'

31dt4 LIST_ADDR

0000000h r

w DMA Transfer List Base Address

Register:

GDMA_MAIN_CTRL

Address:

8h

Bits:

31dt0

Reset value:

00000000h

Attributes: r (w)

Description:

Main Control register

Bit

Identifier

Reset

Attr. Function

/

Description

0dt0 DMA_EN

0h

r w Global

Enable

1dt1 SW_RESET

0h

r w

Software Reset

'0' = don’t care, '1' = Reset

14dt2 <notused>

00h

r

all bits

= '0'

15dt15 JC_RESET

0h

r w

Reset Job Counter

'0' = don’t care, '1' = Reset

16dt16 ERR_INT_EN

0h

r w Error Interrupt Enable