Copyright © Siemens AG 2016. All rights reserved

61

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

the EOI register. The ICU recognizes this and deletes the corresponding bit from

the in-service register and also simultaneously cancels the above-mentioned flag.

2.3.2.13.4 Operating rules

Reconfiguration of priorities

Although the ICU can handle the same priorities for several interrupts, the following has

to be taken into account for the reconfiguration: The reconfiguration of priorities is only

permissible when there are no interrupts "in service" anymore. To ensure that no unfore-

seen event occurs during that time, the software has to mask both interrupts having the

same priority.

Level-sensitive interrupts

It has to be taken into account that a level-sensitive interrupt is acknowledged at its

source (i.e. the level reset there) before it is acknowledged on the software side. This is

necessary because otherwise another entry would be made in the interrupt request regis-

ter for this interrupt.

Acknowledgement of the INTBs with write access to acknowledge register

The software also has the option of carrying out the acknowledgement of the INTB inter-

rupt via a write access to the INTBACK register. For that it has to be noted that this write

access is destructive and the number of the fast interrupt which triggered the interrupt on

the CPU is lost irrevocably. Therefore, in this operating mode, the CPU has to know ex-

actly who triggered the fast interrupt.

Using INTAs as INTBs

INTA and INTB always have to be set to the same triggering. This is not checked by the

ICU and has to be ensured by the software. Moreover, the SW should normally mask the

INTA input in the INTA sub-block used as INTB since otherwise an INTA as well as an

INTB is signaled to the CPU upon the occurrence of the interrupt.

Identical priorities

Identical priorities are intercepted by the ICU as follows: If interrupts have the same priori-

ty, the interrupt number is used as the second priority level, whereby the following ap-

plies: The lower interrupt number has a higher priority than the higher interrupt number.

The following nevertheless applies additionally: If an interrupt is already processed by the

CPU, it cannot be interrupted by another interrupt of the same priority. Only when the first

one has been executed and the next pending interrupt is still the one of the same priority,

is this interrupt processed.

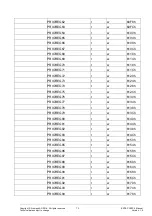

Hardware latencies in certain back2back software accesses

Due to hardware latencies, an old and wrong data item might be read back in the follow-

ing back2back accesses (described is a writing on the first and immediate reading of the

second register):

IRCLVEC -> ACK

IRCLVEC -> IRREG1-5

IRCLVEC -> SWIRREG1-5

LOCKREG -> ACK

MASK -> ACK

ACK->IRREG1-5