Copyright © Siemens AG 2016. All rights reserved

345

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

2.3.10.7.6 Address

Mapping

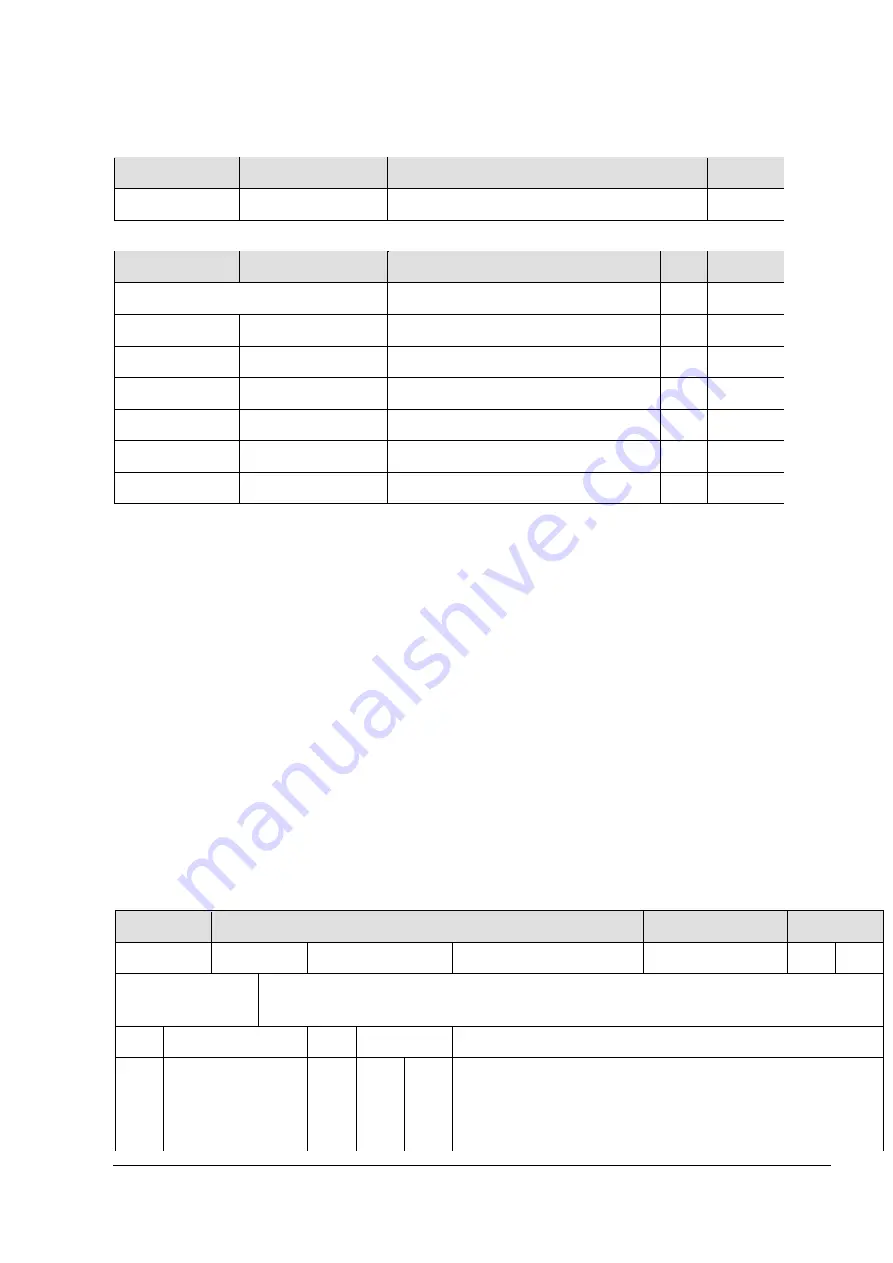

Start_Address End_Address

Modul/Memory_Name

Interface

0h

14h

SPI

APB

Module

Register/Memory Read

Write Address

/SPI

SSPCR0

r

w 0h

SSPCR1

r

w 4h

SSPDR

rh

w 8h

SSPSR

r

Ch

SSPCPSR

r

w 10h

SSPIIR_SSPICR rh

14h

2.3.10.7.7 Register Description

Only the registers with addresses 0 – 14h are required for operating the SSPMS IP. The

remaining registers (addresses 20h – B0h) are created by mirroring (address bit 5 of the

APB bus is not connected to the SSPMS IP) or are only implemented for verification

purposes.

Note on read values for unassigned register bits

In the description of the SSPMS IP, the read value of the unassigned register bits is given

as "unpredictable". A read value of 0 is, however, implemented (see SspApbif.vhd, as-

signment to the NextPRDATA signal).

A description of the registers can be found in the SSPMS IP documentation:

The data-bus-width of all specified registers in this module is: 32.

A '0' is read from Software for each not specified Bit in the registers.

The addressing is organized: WORD – wise

Register:

SSPCR0

Address:

0h

Bits:

15dt0

Reset value:

0h

Attributes:

r

w

Description:

SSPCR0 is control register 0 and contains five bit fields that control various

functions within the PrimeCell SSPMS.

Bit Identifier

Reset Attr.

Function / Description

3dt0 DSS

0h r

w

Data size select:

0000 Reserved, undefined operation

0001 Reserved, undefined operation

0010 Reserved, undefined operation