Copyright © Siemens AG 2016. All rights reserved

232

ERTEC 200P-2 Manual

Technical data subject to change

Version 1.0

To flexible adaption of external HW events to Interrupt Management, they can be config-

ured separately over the IRQExt_Event register using

Ext_IRQx_Level

for the active

level. Either level or edge triggering can also be selected with

Ext_IRQx_Edge

.

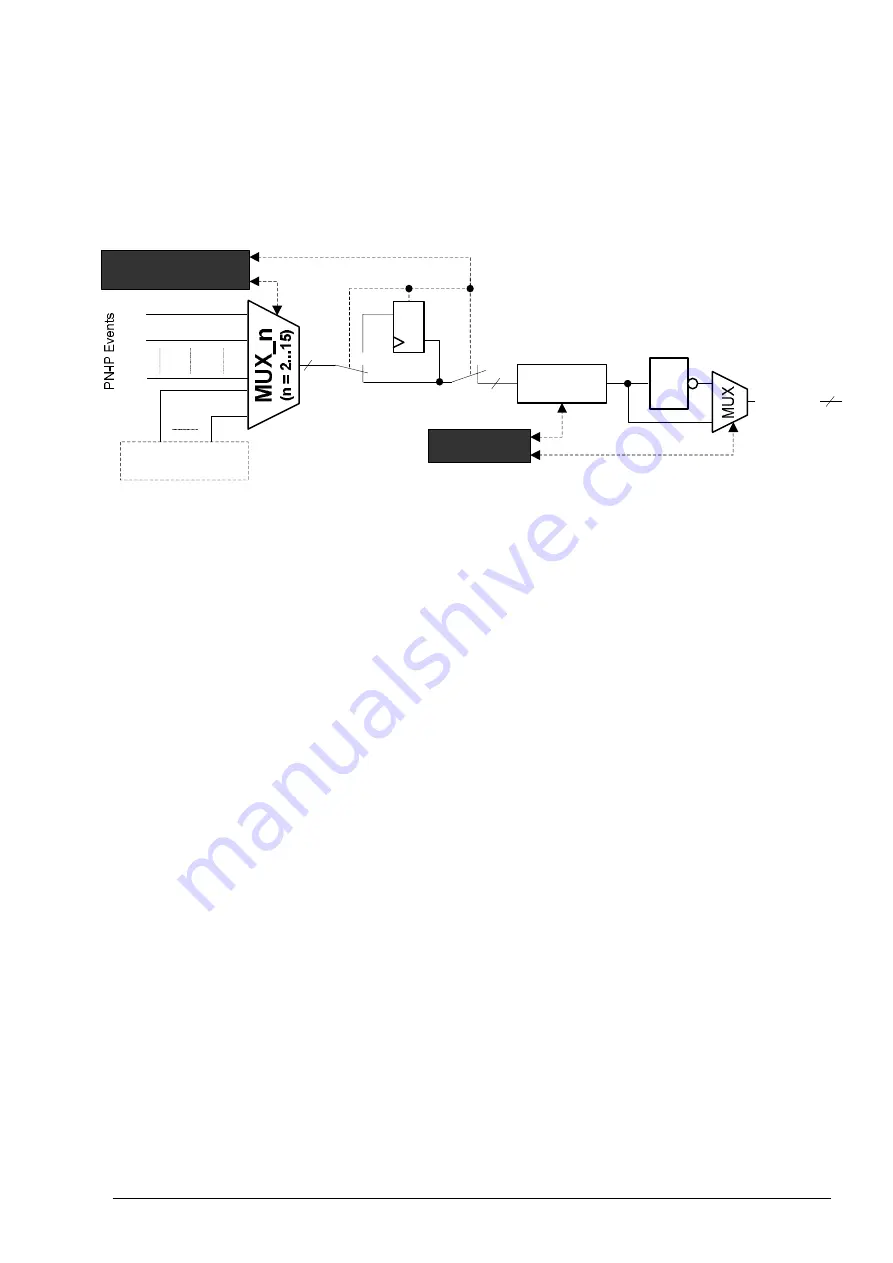

PN-MUX

Each PN_IRQx(

2:1/15:2

) single interrupt is generated as shown here:

0

85

1

IRQ_Activate

60

IRQControl_MUX

(n = 2...15)

IRQ_Control

1

14

IRQ(2:1/15:2)

Pulse

Extension

14

2/14

Virtual

register

Physical

registers

63

D

Reset

Q

IRQ_Level

IRQ_Length

IRQ_SelectMUX

IRQ_WaitTime

Figure 24: Block diagram of PN-MUX for PN_IRQx(2:1/15:2) single interrupts

Event bits 63 - 60 are assigned bits(3:0) from the IRQ_Activate registers to allow a SW

event to be triggered with PN_IRQx(0/1:0) group interrupts and PN_IRQx(2:1/15:2) single

interrupts. Write access to the relevant register bits triggers a SW event as a pulse (8 ns

pulse). Write access in the IRQ_Activate registers is non-retentive. Read access always

returns a value of 0x0000.

For each interrupt output, you can set which PN-IP event or SW event is implemented

externally as a single interrupt over the IRQControl_MUXn register with

IRQ_SelectMUX.

PN-IP event are assigned event numbers (

IRQ_SelectMUX

) in line with the assignment

(bit position) of the PN-IP events in the IRQEvent register.

The interrupt load of the selected single event in the connected CPU subsystems can be

reduced by writing

IRQxControl_MUXn.IRQ_WaitTime

. No new single event (single inter-

rupt) is entered in the external CPU subsystem while

IRQ_WaitTime

is running

(

IRQ_WaitTime

0x000). During this time, the selected events are buffered in

IRQxCon-

trol_MUXn.IRQ_Event

and trigger a single interrupt as soon as

IRQ_WaitTime

(

IRQ_WaitTime

= 0x000) is up. At the same time, the value saved in

IRQ_Event

is

cleared. The single event is extended to the configured pulse length

(

IRQx_Control

.

IRQ_Length

) with pulse extension. The current timer value can be read

back with read access. If there is another instance of read access to

IRQxCon-

trol_MUXn

before

IRQ_WaitTime

is up, the newly written value is used as

IRQ_WaitTime

.

This allows

IRQ_WaitTime

to be extended or shortened by writing the SW in time.

As long as

IRQ_WaitTime

is not written and therefore not used (i.e.

IRQ_WaitTime

=

0x000, default value), the selected single event (single interrupt) is connected straight to

the relevant CPU subsystems (combinatorial).

2.3.8.1.3 PN-PLL (incl. 3x Application Timer Blocks)