Chapter 3 Signals

3-3

3.1.3

External Interface Signals

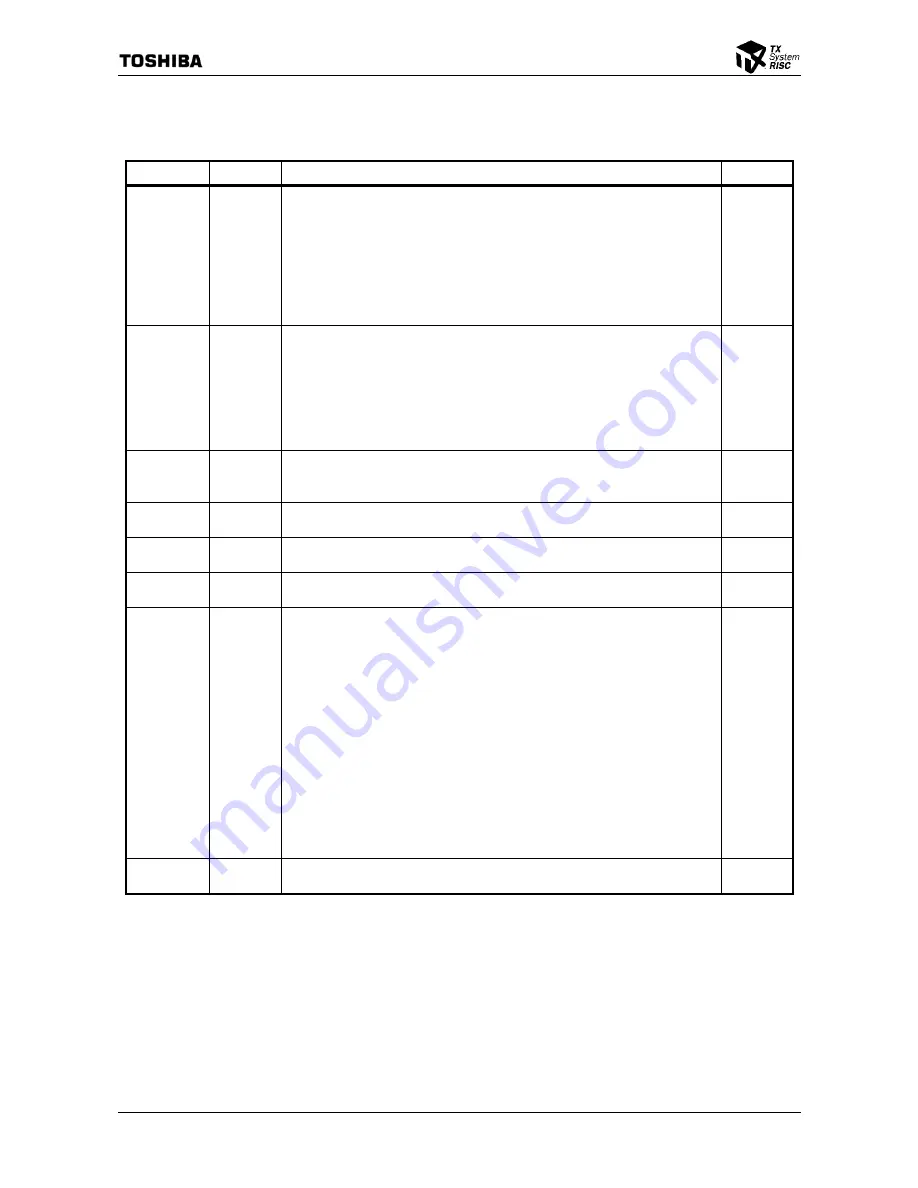

Table 3.1.3 External Interface Signals (1/2)

Signal Name

Type

Description

Initial State

SYSCLK Output

System

Clock

Clock for external I/O devices.

Outputs a clock in full speed mode (at the same frequency as the G-Bus clock

(GBUSCLK) frequency), half speed mode (at one half the GBUSCLK frequency), third

speed mode (at one third the GBUSCLK frequency), or quarter speed mode (at one

quarter the GBUSCLK frequency). The boot configuration signals on the ADDR[4:3]

pins select which speed mode will be used.

When this clock signal is not used, the pin can be set to L using the SYSCLK Enable

bit of the pin configuration register (PCFG.SYSCLKEN).

High

UAE Output

PU

Upper Address Enable

Latch enable signal for the high-order address bits of ADDR. This is a Low active

signal.

This signal is also used as a boot configuration input signal for testing. Because this

signal is used for testing, ensure that it will not pulled Low during a reset sequence.

For details of configuration signals, refer to Section “3.2 Boot Configuration”.

This signal is used as an input signal while the RESET

*

signal is asserted. It becomes

an output signal once the RESET

*

signal has been deasserted.

Input

CE[5:4]

*

Output

PU

Chip Enable

Chip select signals for ROM, SRAM, and I/O devices.

The pins are shared with other functions (refer to Section “3.3 Pin Multiplexing”).

All High

CE[3:0]

*

Output

Chip

Enable

Chip select signals for ROM, SRAM, and I/O devices.

All High

OE

*

Output

Output

Enable

Output enable signal for ROM, SRAM, and I/O devices.

High

SWE

*

Output

Write

Enable

Write enable signal for SRAM and I/O devices.

High

BWE[3:0]

*

/BE[3:0]

*

Output

Byte Enable/Byte Write Enable

BE[3:0]

*

indicate a valid data position on the data bus DATA[31:0] during read and

write bus operation. In 16-bit bus mode, only BE[1:0]

*

are used. In 8-bit bus mode,

only BE[0]

*

is used.

BWE[3:0]

*

indicate a valid data position on the data bus DATA[31:0] during write bus

operation. In 16-bit bus mode, only BWE[1:0]

*

are used. In 8-bit bus mode, only

BWE[0]

*

is used.

The following shows the correspondence between BE[3:0]

*

/BWE[3:0]

*

and the data

bus signals.

BE[3]

*

/BWE[3]

*

: DATA[31:24]

BE[2]

*

/BWE[2]

*

: DATA[23:16]

BE[1]

*

/BWE[1]

*

: DATA[15:8]

BE[0]

*

/BWE[0]

*

: DATA[7:0]

The boot configuration signal on the ADDR[11] pin and the EBCCRn.BC bit of the

external bus controller determine whether the signals are used as BE[3:0]

*

or

BWE[3:0]

*

.

All High

ACK

*

/ READY Input/output

PU

Data Acknowledge/Ready

Flow control signal (refer to Section “7.3.6 Access Modes”).

Input

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...