Chapter 14 AC-link Controller

14-17

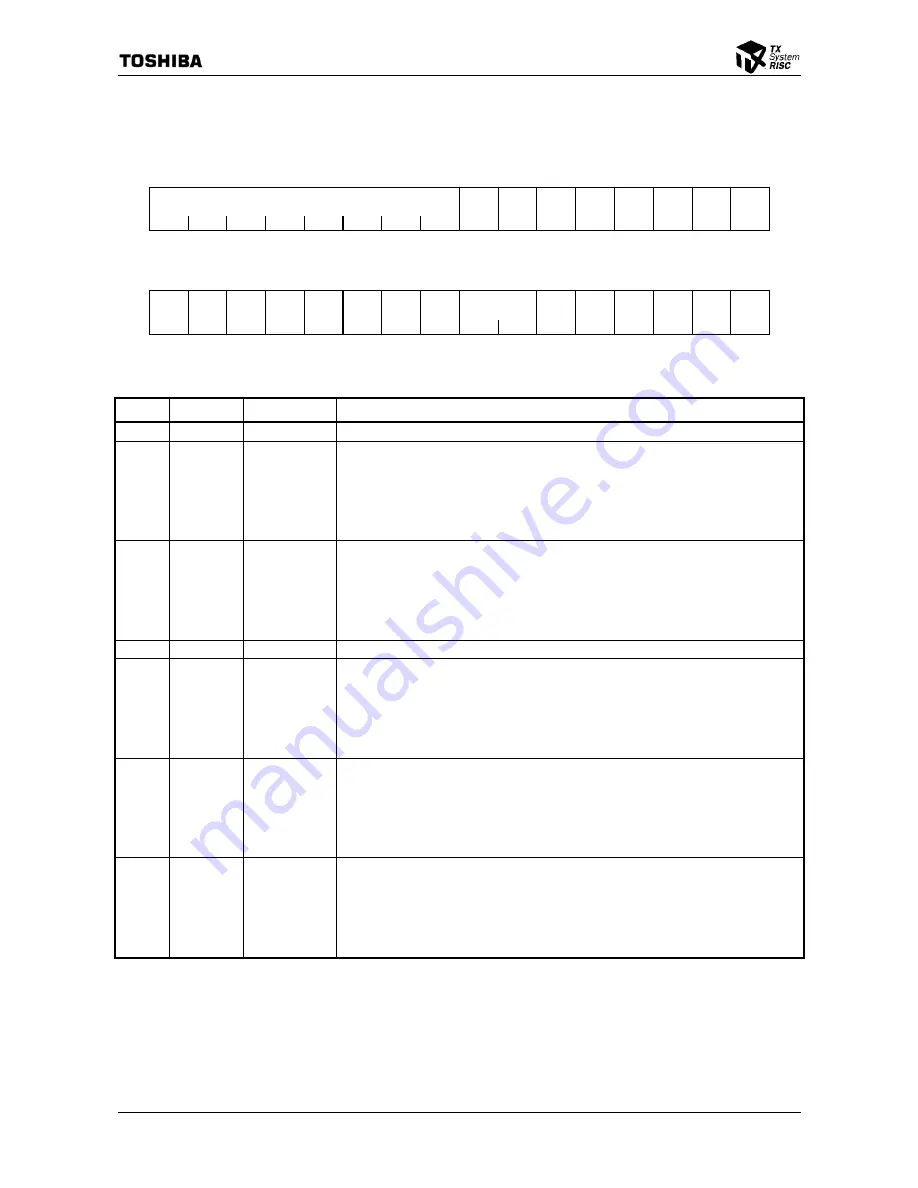

14.4.1 ACLC Control Enable Register (ACCTLEN)

0xF700

This register is used to check the setting of various ACLC features and to enable them.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

MODIE

HLT

MODOE

HLT

Reserved

AUDIE

HLT

LFEEH

LT

CENTE

HLT

SURRE

HLT

AUDO

EHLT

R/W1S R/W1S

R/W1S R/W1S

R/W1S

R/W1S

R/W1S

: Type

0

0 0

0

0

0

0

:

Initial

value

15

14

13

12

11

10 9 8 7 6 5 4 3 2 1 0

MODID

MA

MODO

DMA

Reserved

AUDID

MA

LFEDM

A

CENTD

MA

SURR

DMA

AUDO

DMA

Reserved

RDYCLR MICSEL WRESET

WAKEUP

LOW

PWR

ENLINK

R/W1S

R/W1S

R/W1S

R/W1S

R/W1S

R/W1S R/W1S

W1C

R/W1S R/W1S

R/W1S

R/W1S

R/W1S

: Type

0 0 0 0 0 0 0

⎯

0 0 0 0 0

:

Initial

value

Bits Mnemonic Field

Name

Description

31:24

⎯

Reserved

⎯

Enable Modem Receive-data DMA Error Halt. (Initial value: 0, R/W1S)

23 MODIEHLT

Enable Modem

Receive-data

DMA Error Halt

R

0: Indicates that MODIDMA error halt is disabled.

1: Indicates that MODIDMA error halt is enabled.

W1S

0:

No

effect

1: Enables MODIDMA error halt. When MODIDMA overrun occurs, subsequent

DMA will not be issued.

Enable Modem Transmit-data DMA Error Halt. (Initial value: 0, R/W1S)

22 MODOEHLT

Enable Modem

Transmit-data

DMA Error Halt

R

0: Indicates that MODODMA error halt is disabled.

1: Indicates that MODODMA error halt is enabled.

W1S

0:

No

effect

1: Enables MODODMA error halt. When MODODMA underrun occurs, subsequent

DMA will not be issued.

21

⎯

Reserved

⎯

Enable Audio Receive-data DMA Error Halt. (Initial value: 0, R/W1S)

20 AUDIEHLT

Enable Audio

Receive-data

DMA Error Halt

R

0: Indicates that AUDIDMA error halt is disabled.

1: Indicates that AUDIDMA error halt is enabled.

W1S

0:

No

effect

1: Enables AUDIDMA error halt. When AUDIDMA overrun occurs, subsequent

DMA request will not be issued.

Enable Audio LFE Transmit-data DMA Error Halt. (Initial value: 0, R/W1S)

19 LFEEHLT

R

0: Indicates that LFEDMA error halt is disabled.

1: Indicates that LFEDMA error halt is enabled.

Enable Audio

LFE

Transmit-data

DMA Error Halt

W1S 0:

No

effect

1: Enables LFEDMA error halt. When LFEDMA underrun occurs, subsequent DMA

request will not be issued.

Enable Audio Center Transmit-data DMA Error Halt. (Initial value: 0, R/W1S)

18 CENTEHLT

R

0: Indicates that CENTDMA error halt is disabled.

1: Indicates that CENTDMA error halt is enabled.

Enable Audio

Center

Transmit-data

DMA Error Halt

W1S 0:

No

effect

1: Enables CENTDMA error halt. When CENTDMA underrun occurs, subsequent

DMA request will not be issued.

Figure 14.4.1 ACCTLEN Register (1/3)

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...