311

CHAPTER 18 I

2

C BUS MODE (

µ

PD784225Y SUBSERIES ONLY)

User’s Manual U12697EJ3V0UM

18.5.4 Acknowledge signal (ACK)

The acknowledge signal verifies the reception of the serial data on the transmitting and receiving sides.

The receiving side returns the acknowledge signal each time 8-bit data is received. Usually, after transmitting 8-

bit data, the transmitting side receives an acknowledge signal. However, if the master receives, the acknowledge

signal is not output when the last data is received. After an 8-bit transmission, the transmitting side detects whether

the receiving side returned an acknowledge signal. If an acknowledge signal is returned, the following processing

is performed assuming that reception was correctly performed. Since reception has not been performed correctly

if the acknowledge signal is not returned from the slave, the master outputs the stop condition to stop transmission.

If an acknowledge signal is not returned, the following two causes are considered.

<1> The reception is not correct.

<2> The last data has been received.

When the receiving side sets the SDA0 line low at the ninth clock, the acknowledge signal becomes active (normal

reception response).

If bit 2 (ACKE0) = 1 in I

2

C bus control register 0 (IICC0), the enable automatic generation of the acknowledge signal

state is entered.

Bit 3 (TRC0) in I

2

C bus status register 0 (IICS0) is set by the data in the eighth bit following the 7-bit address

information. However, set ACKE0 = 1 in the reception state when TRC0 bit is 0.

When the slave is receiving (TRC0 = 0), the slave side receives multiple bytes and the next data is not required,

when ACKE0 = 0, the master side cannot start the next transfer.

Similarly, the next data is not needed when the master is receiving (TRC0 = 0), set ACKE0 = 0 so that the ACK

signal is not generated when you want to output a restart or stop condition. This prevents the output of MSB data

in the data on the SDA0 line when the slave is transmitting (transmission stopped).

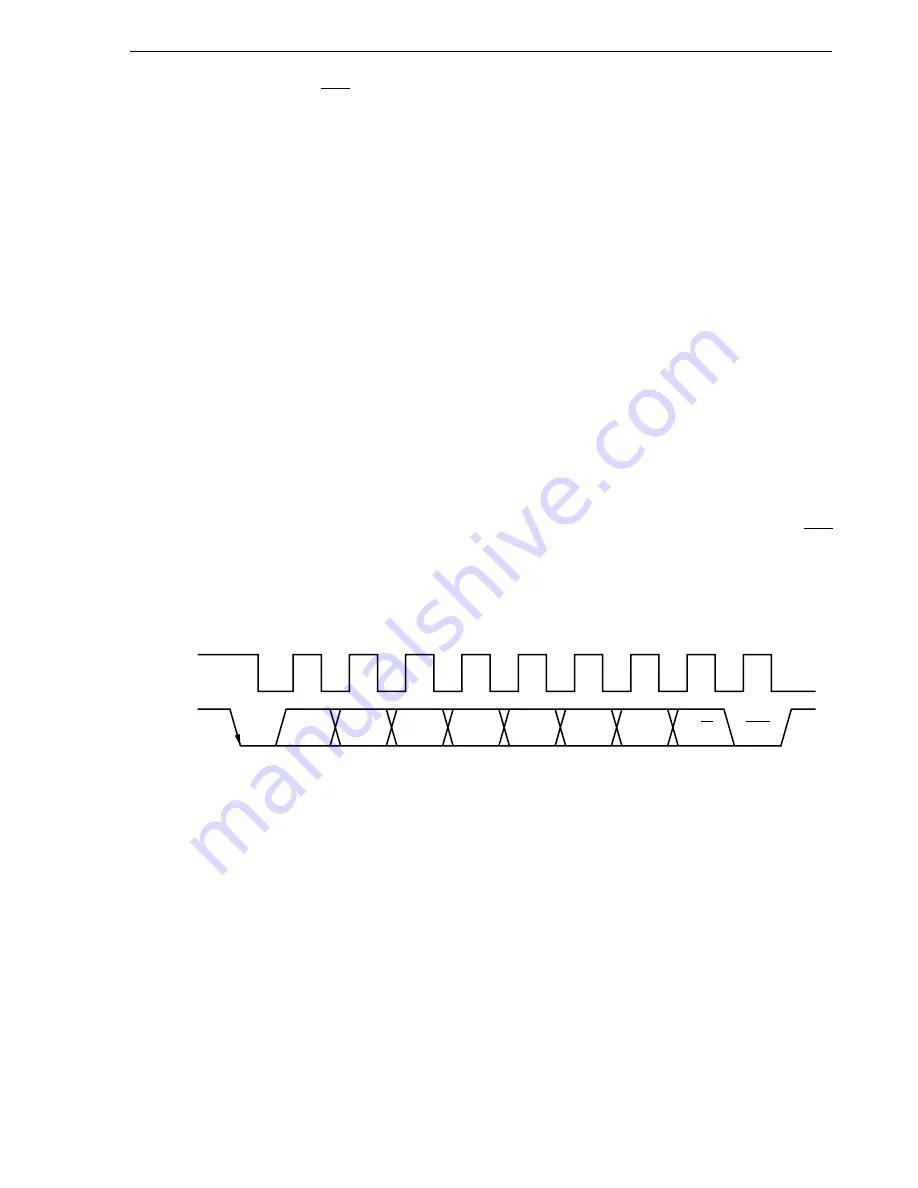

Figure 18-11. Acknowledge Signal

SCL0

SDA0

1

2

3

4

5

6

7

8

9

A6

A5

A4

A3

A2

A1

A0

R/W

ACK

When receiving the base address, the automatic output of the acknowledge is synchronized to the falling edge

of the eighth clock of SCL0 regardless of the ACKE0 value. When receiving at an address other than the base address,

the acknowledge signal is not output.

The output method of the acknowledge signal when receiving data is as follows based on the wait timing.

•

When 8 clock waits are selected : The acknowledge signal is synchronized to the falling edge of the eighth

clock of SCL output by setting ACKE0 = 1 before the wait is released.

•

When 9 clock waits are selected: By setting ACKE0 = 1 beforehand, the acknowledge signal is synchronized

to the falling edge of the eighth clock of SCL0 and is automatically output.