523

User’s Manual U12697EJ3V0UM

CHAPTER 28 INSTRUCTION OPERATION

28.1 Conventions

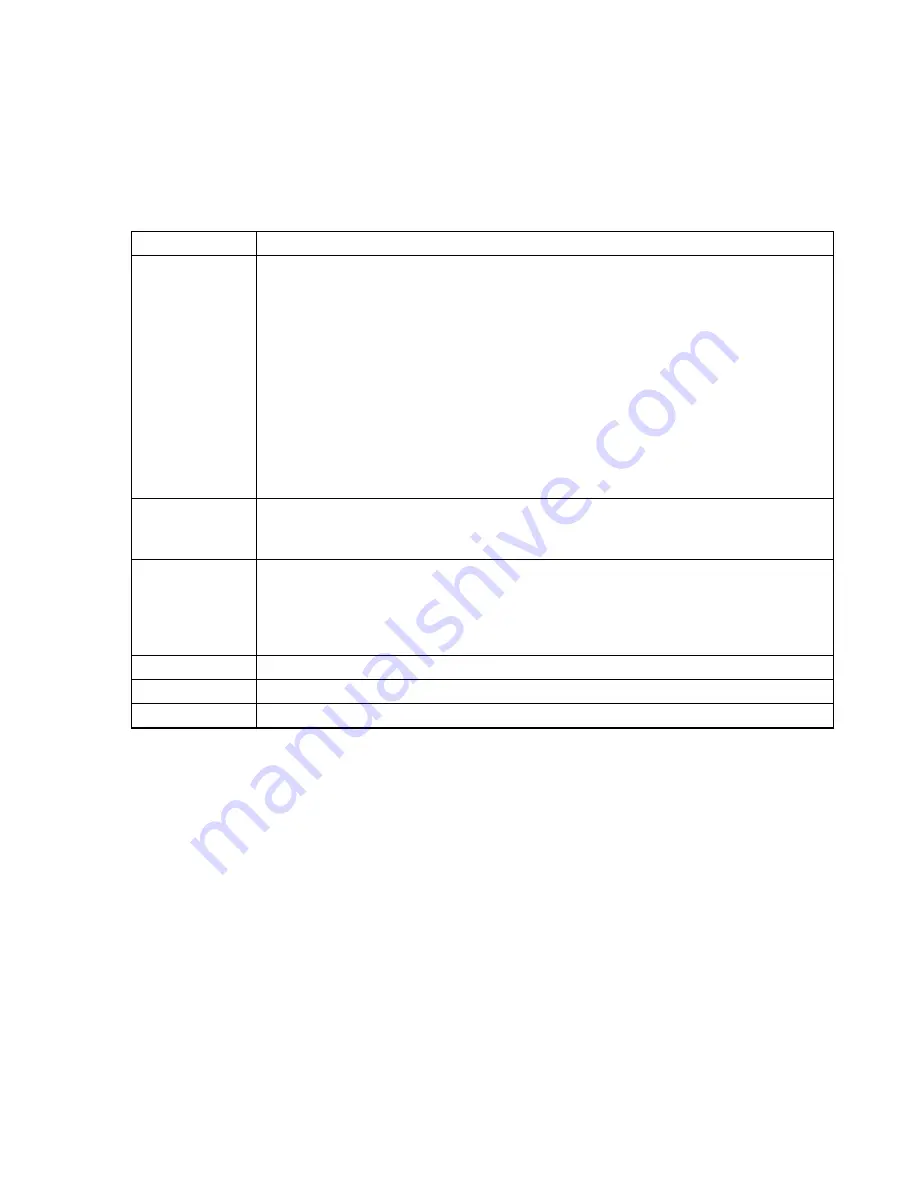

(1) Operand format and descriptions (1/2)

Format

Description

r, r’

Note 1

X(R0), A(R1), C(R2), B(R3), R4, R5, R6, R7, R8, R9, R10, R11, E(R12), D(R13), L(R14), H(R15)

r1

Note 1

X(R0), A(R1), C(R2), B(R3), R4, R5, R6, R7

r2

R8, R9, R10, R11, E(R12), D(R13), L(R14), H(R15)

r3

V, U, T, W

rp, rp’

Note 2

AX(RP0), BC(RP1), RP2, RP3, VP(RP4),UP(RP5), DE(RP6), HL(RP7)

rp1

Note 2

AX(RP0), BC(RP1), RP2, RP3

rp2

VP(RP4), UP(RP5), DE(RP6), HL(RP7)

rg, rg'

VVP(RG4), UUP(RG5), TDE(RG6), WHL(RG7)

sfr

Special function register symbol (see the special function register table)

sfrp

Special function register symbol (16-bit manipulation register: see the special function register table)

post

Note 2

AX(RP0), BC(RP1), RP2, RP3, VP(RP4), UP(RP5)/PSW, DE(RP6), HL(RP7)

Multiple descriptions are possible. However, UP is restricted to the PUSH/POP instruction, and

PSW is restricted to the PUSHU/POPU instruction.

mem

[TDE], [WHL], [TDE+], [WHL+], [TDE– ], [WHL– ], [VVP], [UUP]: register indirect addressing

[TDE+byte], [WHL+byte], [SP+byte], [UUP+byte], [VVP+byte]: based addressing

imm24[A], imm24[B], imm24[DE], imm24[HL]: indexed addressing

[TDE+A], [TDE+B], [TDE+C], [WHL+A], [WHL+B], [WHL+C], [VVP+DE], [VVP+HL]: based indexed

addressing

mem1

Everything under mem except [WHL+] and [WHL–]

mem2

[TDE], [WHL]

mem3

[AX], [BC], [RP2], [RP3], [VVP], [UUP], [TDE], [WHL]

Notes 1.

By setting the RSS bit to one, R4 to R7 can be used as X, A, C, and B. Use this function only when

78K/III Series programs are also used.

2.

By setting the RSS bit to one, RP2 and RP3 can be used as AX and BC. Use this function only when

78K/III Series programs are also used.