365

CHAPTER 22 INTERRUPT FUNCTIONS

User’s Manual U12697EJ3V0UM

22.3 Interrupt Servicing Control Registers

µ

PD784225 interrupt servicing is controlled for each interrupt request by various control registers that perform

interrupt servicing specification. The interrupt control registers are listed in Table 22-3.

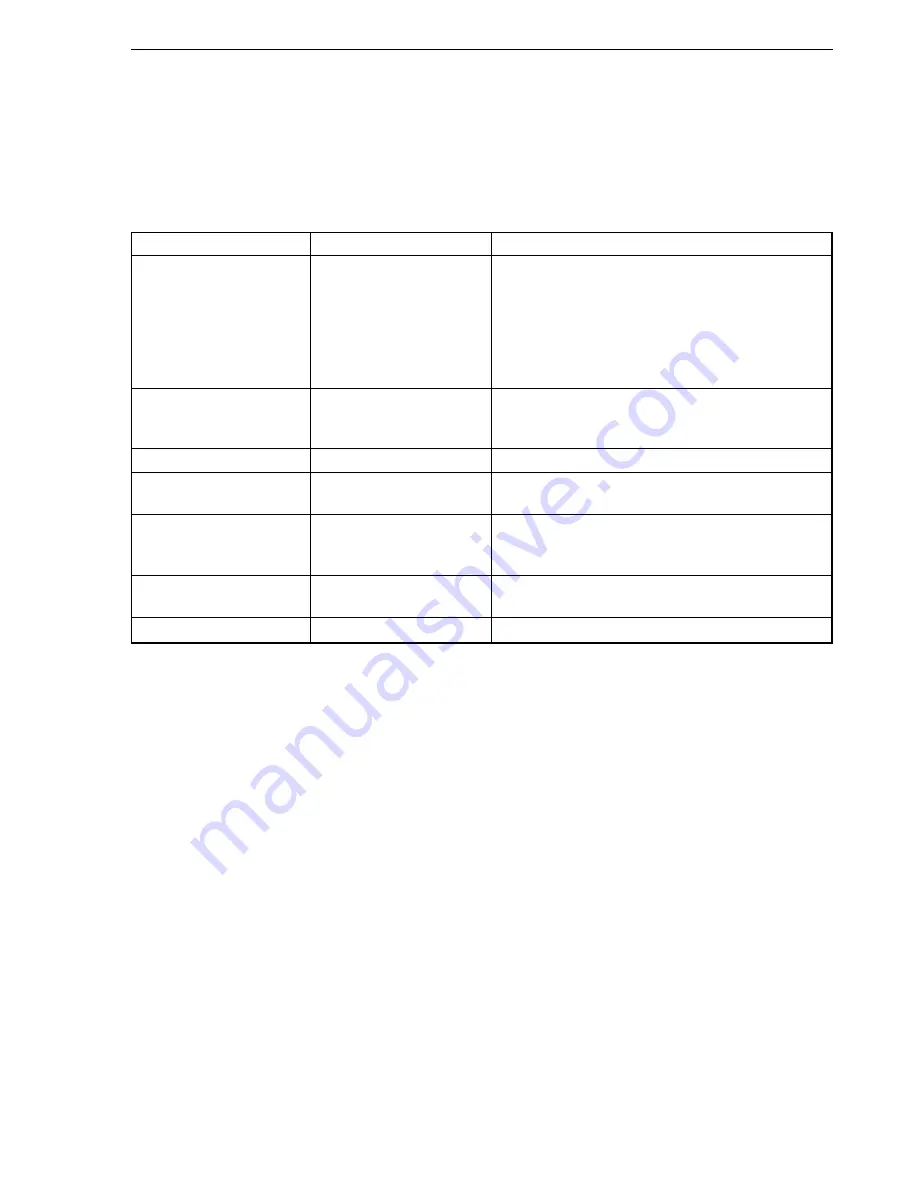

Table 22-3. Control Registers

Register Name

Symbol

Function

Interrupt control registers

WDTIC, PIC0, PIC1, PIC2,

Registers to record generation of interrupt request, control

PIC3, PIC4, PIC5, CSIIC0,

masking, specify vectored interrupt servicing or macro

SERIC1, SRIC1, STIC1,

service processing, enable or disable context switching

SERIC2, SRIC2, STIC2,

function, and specify priority.

TMIC3, TMIC00, TMIC01,

TMIC1, TMIC2, ADIC,

TMIC5, TMIC6, WTIC

Interrupt mask registers

MK0 (MK0L, MK0H)

Control masking of maskable interrupt request. Associated

MK1 (MK1L, MK1H)

with mask control flag in interrupt control register. Can be

accessed in word or byte units.

In-service priority register

ISPR

Records priority of interrupt request currently accepted.

Interrupt mode control register

IMC

Controls nesting of maskable interrupt with priority specified

to lowest level (level 3).

Interrupt selection control

SNMI

Selects whether to use input signal from P02 pin and

register

interrupt signal from watchdog timer as maskable interrupt

or NMI.

Watchdog timer mode register

WDM

Specifies priorities of interrupt by NMI pin input and

overflow of watchdog timer.

Program status word

PSW

Enables or disables accepting maskable interrupt.

An interrupt control register is allocated to each interrupt source. The flags of each register perform control of the

contents corresponding to the relevant bit position in the register. The interrupt control register flag names

corresponding to each interrupt request signal are shown in Table 22-4.